# PART I General

- Design Objectives

Hardware Overview

- 3. Algorithms and Performance

# Part I Chapter 1

# **DESIGN OBJECTIVES**

# I.1.1 System Goals

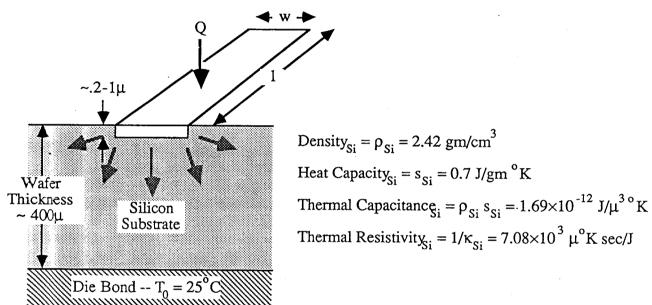

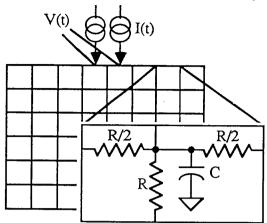

We are designing Pixel-planes 5 to be an interesting research vehicle for high performance 3-D graphics architecture, an experiment in design and construction of high performance digital systems, and a platform for graphics algorithms research. We describe here the overall objectives in the Pxpl5 design, listed roughly in order of importance:

- Fast Polygon Rendering. For Pxpl5 to be an interesting research vehicle it must offer substantially higher performance than available commercial machines. We believe that performance in excess of 1M Phong-shaded z-buffered triangles per second (we assume 100-pixel triangles embedded in triangle strips) will be required to meet this objective by mid 1989. In addition to advanced lighting models with multiple lights, texturing and anti-aliasing will be considered essential in interactive raster graphics systems; we expect to provide these enhancements with no worse than 10x penalty in performance.

- Programmability. To be useful as a research vehicle, Pxpl5 must be easy to program, and all of its power should be available from a high-level language. We believe that C-language support and a graphics support library are essential to the development of new graphics algorithms. We are becoming convinced that compatibility with a subset of the PHIGS+ graphics standard will be useful; we have found from the Pxpl4 experience that familiar standards are very helpful for ease of use. Network extensibility via a subset of X.11 is desirable.

- Packaging. Pxpl5 will be modular and re-configurable in a variety of forms that trade performance for cost. A very high-performance configuration that meets our primary performance goals must fit within a workstation pedestal and should consume no more than 2KW of power. These limits allow the machine to live in an office environment.

- Curved Surfaces. While the machine's primary performance goal is expressed in terms of processing polygonal data, it is desirable that more expressive, more efficient graphics primitives be supported. We intend to provide a machine that can directly render certain curved surfaces and that provides at least rapid tesselation of surfaces described by B-splines.

- Constructive Solid Geometry. The new platform should provide a basis for greatly extending the speed and usefulness of our current work in editing and displaying objects described by CSG.

- Volumetric and Image Processing Algorithms. There is considerable local research in volumetric displays and in image processing; we want to support this work by providing a fast and flexible platform on which images can be displayed rapidly and also transformed in a variety of ways.

#### I.1.2 Architectural Features

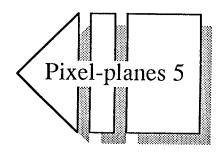

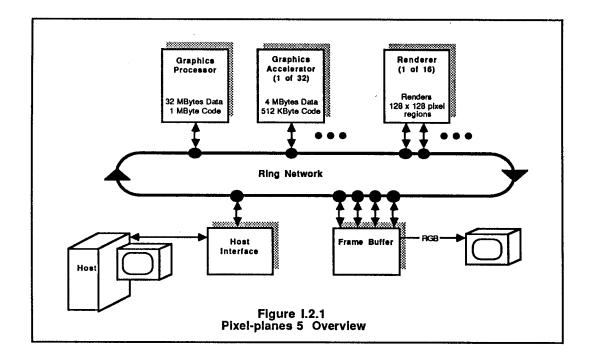

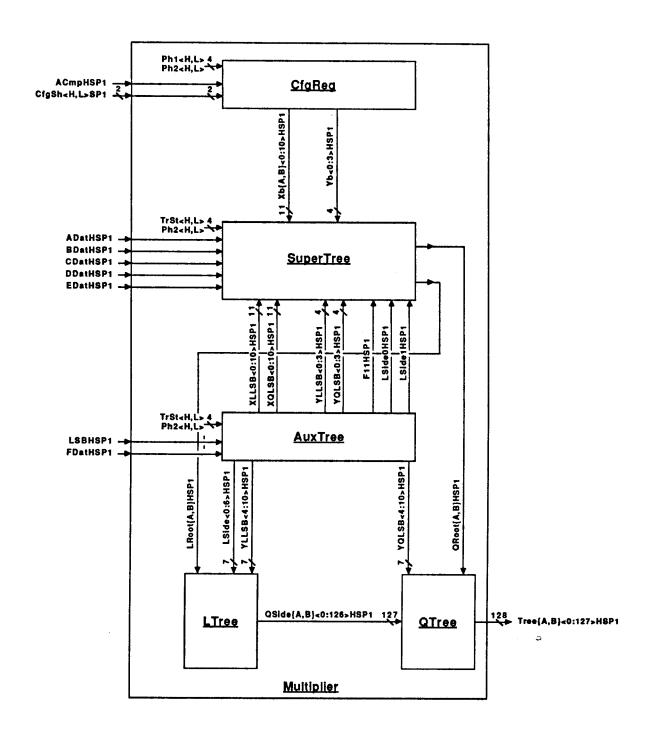

Since Pxpl5 is intended as an experimental platform for parallel processing in graphics and image processing. Its architecture is quite general, consisting of a collection of two types of processing elements, Graphics Processors (GP's) and Renderers, that communicate over a Ring network. The Ring also connects these elements to a display device and a Host workstation. A Pxpl5 system may be configured with varying numbers of GP's and Renderers to meet diverse computational and budget needs.

We describe here how the GP's and Renderers carry out, respectively, the object-oriented and pixel-oriented computation tasks in a graphics system. These processors are not, however, limited to these tasks. For example, a Renderer may be viewed as a very powerful SIMD machine capable of attacking other computing problems encountered in Ray Tracing, Image Processing, and elsewhere.

The "front end" of typical raster graphics systems deals with compact descriptions of objects to be displayed. It traverses hierarchical display lists that describe these objects, performs geometric transformations and clipping, and computes various lighting effects. Pxpl5 performs these computations with a collection of GP's operated in MIMD fashion. The general purpose nature of these processors is necessary for a variety of algorithms, including ones that sort primitives into bins corresponding to small contiguous regions of the display screen, a step crucial in applying the Renderers in parallel to the "back end" problem.

The "back end" or "renderer" of a raster system is responsible for the pixel-oriented operations of scan conversion (determining which pixels are inside a given graphics primitive), hidden-surface elimination (determining which pixels of an object are visible and which are hidden by other objects), and shading (painting color onto the pixels in such a way as to give the appearance of a "real" surface). In most raster systems the pixel color values from these computations are written into a "frame buffer" memory, from which the display is refreshed. Pxpl5's set of Renderers performs these computations with SIMD parallelism at the pixel level and coarse-grain, MIMD parallelism at the level of small, disjoint regions of the screen.

The major elements, then, of the Pxpl5 design are:

- Graphics Processors (GP's), floating point engines, each with considerable local code and data storage.

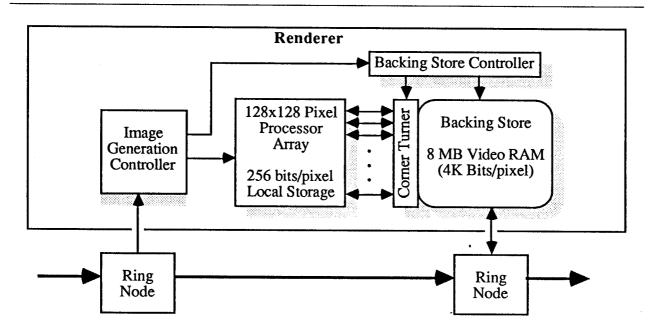

- Renderers, each a small SIMD array of pixel processors with its own controller.

- Frame Buffer, double-buffered, built from conventional Video RAM's, from which the display is refreshed.

- Host Interface, which supports communications to/from a UNIX workstation.

The initial configuration of the system will likely have 32 GP's, 8-16 Renderers, a Host Interface and a Frame Buffer. A useful system can be built with as few as one GP, one Renderer, a Host Interface and a Frame Buffer. We discuss these elements in more detail below.

# **Ring Network**

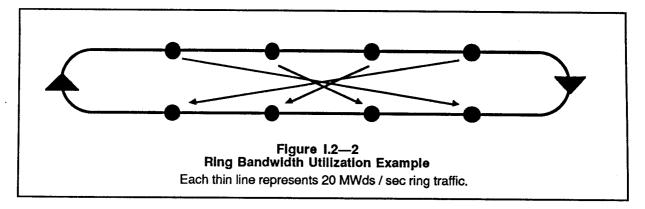

The bandwidth required to move primitive object descriptions from the "front end" to the renderer in our system will reach 40 MWords/second, even for relatively simple rendering algorithms. Simultaneously, pixel values must be moved from the renderer to a frame buffer at rates up to 60 MWords/sec for real-time interactive applications. Pxpl5 will have a single, unified communications structure to support both kinds of traffic. For the very large bandwidth required, a simple bus is not practical for technological reasons, so we employ a ring network in Pxpl5. The Ring is physically concentrated onto a single printed circuit board, with only short point-to-point communications paths between Ring Nodes, and can therefore be operated at quite high speeds between nodes. Initial specifications call for a one-word-wide (32 bits of data) Ring operating at 160 MHz.

Each Ring Node is a separate custom integrated circuit that serves a client board (a Ring Device) with a single 20 MHz bi-directional port. The Ring protocol allows multiple messages to be present on the Ring at one time, so each Ring Device can send a message to another Device at 20 MWords/second, even when many pairs of Devices are communicating simultaneously.

For many applications, the multiple GP's in a system will be used mainly to implement the "front end" functions, while the Renderers perform pixel-oriented operations. However, the Ring connects these elements in a very general way, so that the machine should be thought of as a heterogeneous array of parallel processors that can be used in a variety of ways.

Figure 1: Overview of Pxpl5 System, showing Ring Network and Ring Devices that include Graphics Processors (GP's), Renderers, Host Interface, and Frame Buffer.

# **Graphics Processors (GP's)**

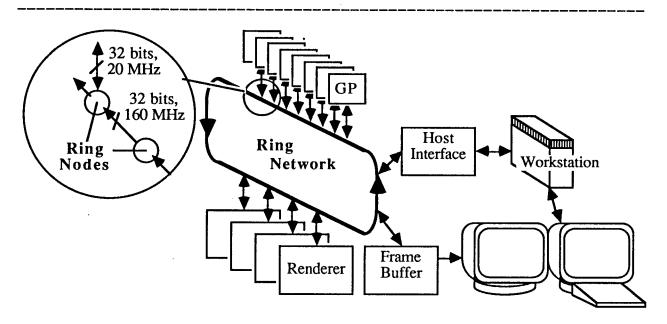

The performance levels we have set require sustained computation rates in the "front end" of several hundred MFlops, feasible today only in parallel or vector architectures. Vector processing offers considerable savings in hardware complexity and cost, but building programming tools for a vector unit is a major undertaking, far beyond the means of our small research group. We have therefore elected to build a MIMD processor based on currently available Weitek "XL" parts. This approach offers three strong advantages:

- The Weitek XL chip set comes with off-the-shelf software support in the form of a C compiler and micro-code assembler.

- Our group has considerable experience with the Weitek XL from building and programming the existing Pxpl4 Graphics Processor (also based on the Weitek XL).

- The general-purpose processors in our MIMD organization can handily sort primitives into bins for Pxpl5's parallel renderer architecture.

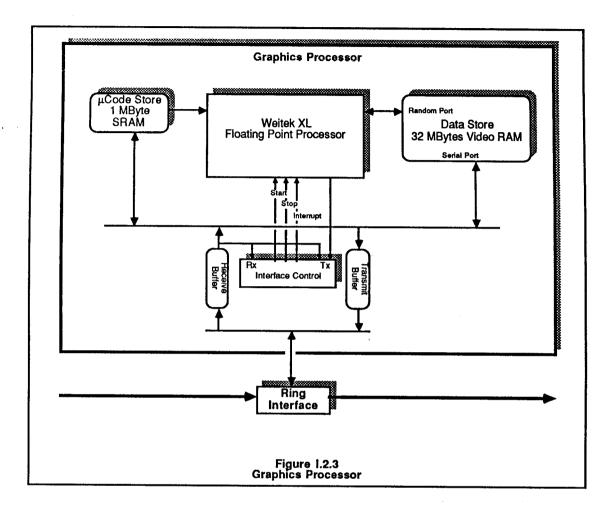

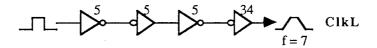

Figure 2: Simplified block diagram of Pxpl5 Graphics Processor.

The programming model can be relatively simple. Load sharing is accomplished by dividing an object database across the GP's, in one of several simple ways, and each GA may run exactly the same code. GP's will be programmable in the C language. So far as possible, users will have access to the machine's full capability without resorting to writing programs in machine code.

#### Renderers

The "back end" of a traditional graphics machine suffers from the well-know memory bandwidth bottleneck into the frame buffer. Even for the simplest shading algorithms, the performance levels we want to attain will require memory bandwidth of 1 GWord/sec or higher (this is based on a simple analysis of memory references needed to render 1M 100-pixel triangles per second). Since this problem has been the focus of our research for many years, we feel that it is essential to demonstrate clearly the strengths of our approach, which is based on frame buffers built from logic-enhanced memories, and to extend this approach as far as possible.

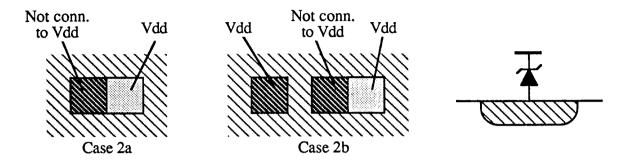

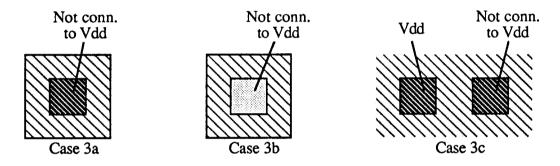

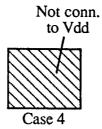

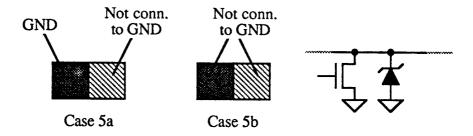

Pxpl4 and previous generations are "fully instantiated" frame buffers—there is a processing element with memory, built onto a custom chip, for each displayed pixel. The screen is refreshed directly from this frame buffer. This simple realization attains performance levels in the range of 50K Gouraud-shaded triangles per second, but it requires over 2,000 custom chips even for a display of modest resolution. To achieve a 20x increase in performance for Pxpl5, to adapt the machine to a variety of new tasks, and to make the design commercially feasible, we require an approach that leverages the speed improvements of better chip technology with an improved renderer architecture:

• Virtual Pixel Architecture. The design of the Renderer in Pxpl5 is intended to overcome the most serious difficulties of the strict SIMD organization of Pxpl4: high cost and poor processor utilization. Improving the utilization of a SIMD array implies getting fewer processors to do more work. We are taking the approach of building multiple Renderers, each a small (perhaps 128x128) array of SIMD pixel processors with its own Image Generation Controller (IGC). Pxpl5 is organized so that each Renderer can operate independently in MIMD fashion on separate stream of graphics primitives, and it is thus parallel by graphics primitive in the Renderer as well as in the "front end". To the extent that successive geometric primitives fall into regions belonging to different Renderers, the system can render those primitives simultaneously. Simulations suggest that this approach may yield 4x or better speedups for complex scenes, which, combined with chip technology improvements, puts us within reach of our performance goals.

This general idea was described in earlier publications as "buffered" Pixel-planes. What is new is the idea of "virtual pixels", a flexible mapping of a Renderer's virtual pixel space onto the space of the display screen. Virtual pixels are supported by a memory hierarchy, whose principal element is the "backing store" described below. A cost of this approach is the sorting problem added to the front end phase: primitives must be sorted into bins corresponding to Renderer-sized regions of the screen, then routed to the appropriate Renderer. The parallel GP's with their large data stores handle this problem nicely.

• Backing Store. To reduce cost, while still achieving very high performance, we will use the Renderers in a completely different way from the single Renderer of Pxpl4. Pxpl5 Renderers are not rigidly assigned to some particular region of the display screen, but can be flexibly mapped to any region. To support this mode of operation, each Renderer has a "backing store" memory, composed of commercial VRAM's, tightly coupled to the EMC's through the VRAM video port. The backing store is available, through the random access port, to the rest of the system, which can read and write pixel values in the conventional way. Soon-available 1MB VRAM's will allow storage of 4K bits per pixel with this organization. A Renderer uses this memory to save and retrieve pixel indicia, effectively allowing "context switches" when the Renderer ceases operating on one part of the screen and moves to another. A typical context switch takes about 0.5 msec, the time required to process a hundred or so

triangles, and can be completely overlapped with processing in the Renderer. For simple applications, the backing store will be used to store pixel color values for sub-regions of the screen as the Renderer completes them. When the entire image has been rendered, each of these regions is transferred in a block to the display memory in the Frame Buffer, from which the display screen is updated. Pxpl5's rendering, then, depends on a three-tiered memory hierarchy: The local, fast memory associated with each pixel processor on the Enhanced Memory Chip is the top-most element in this hierarchy, the backing store is the second tier, and the Frame Buffer is the third. This memory structure allows useful systems to be built with any number of Renderers; a single Renderer with only 64 custom chips, for example, would provide better performance in many applications, and more generality than does Pxpl4.

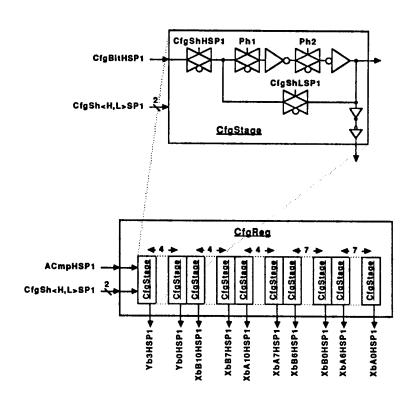

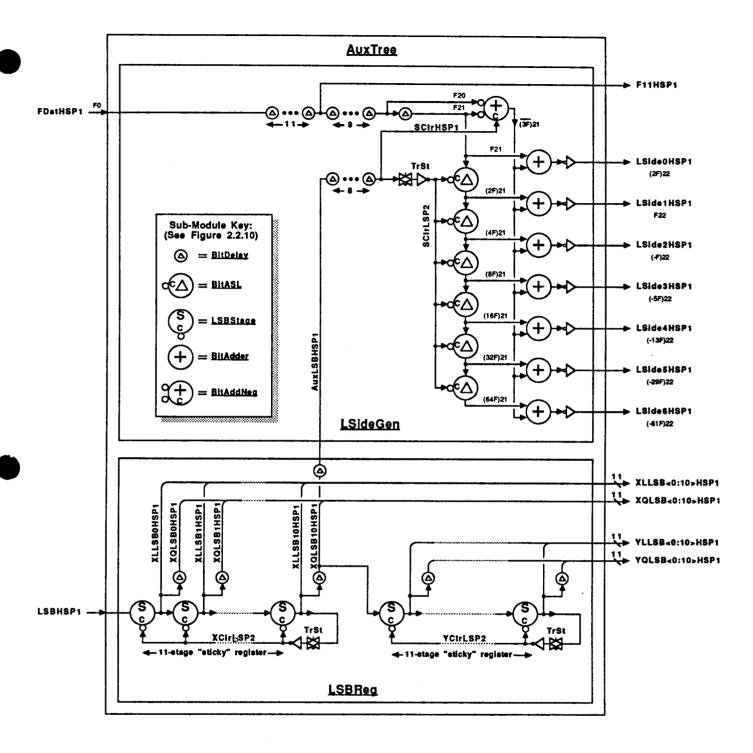

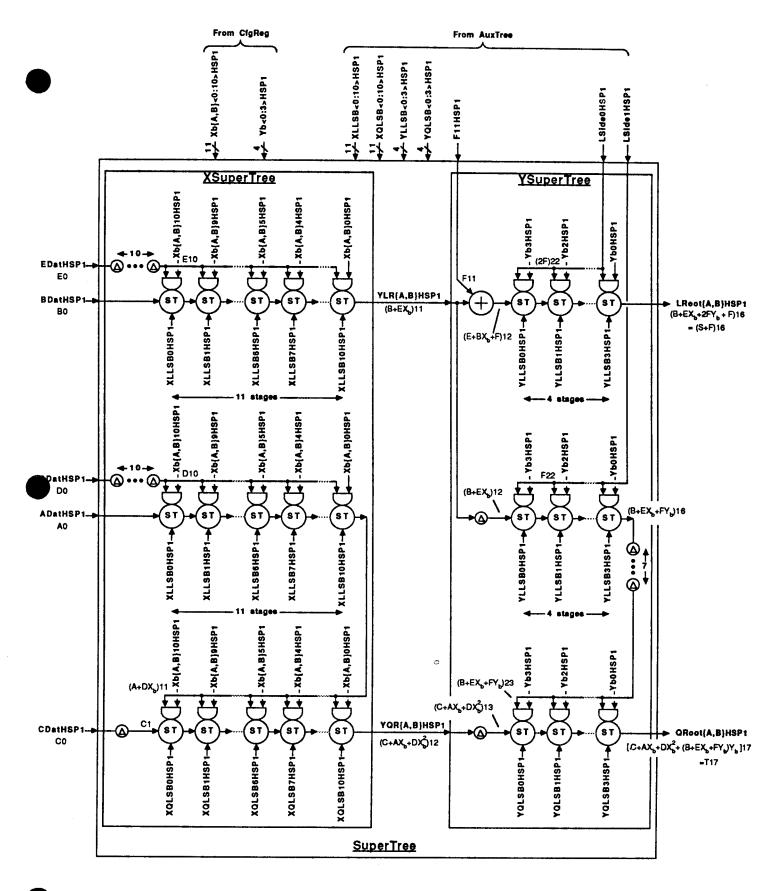

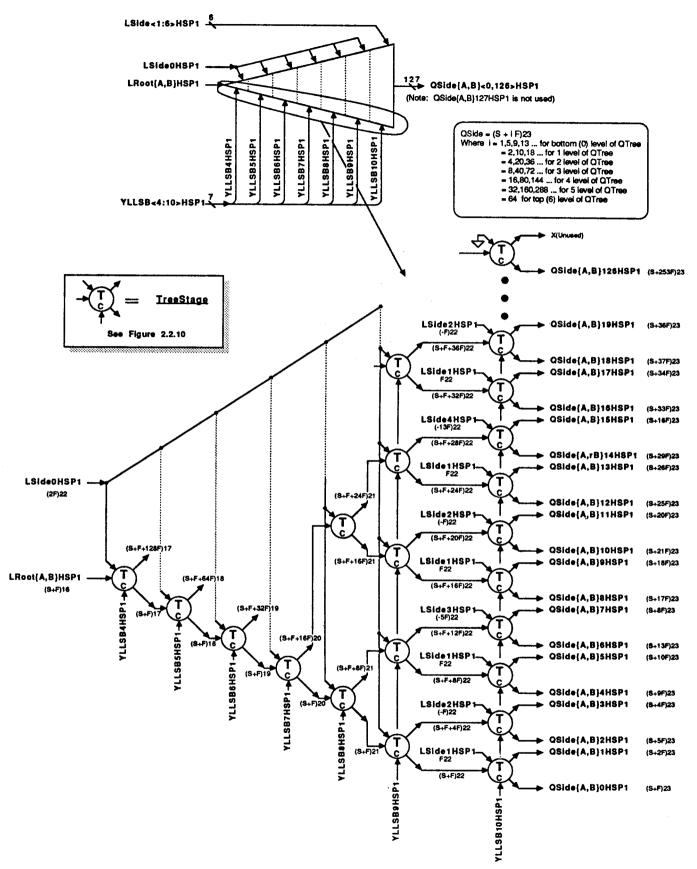

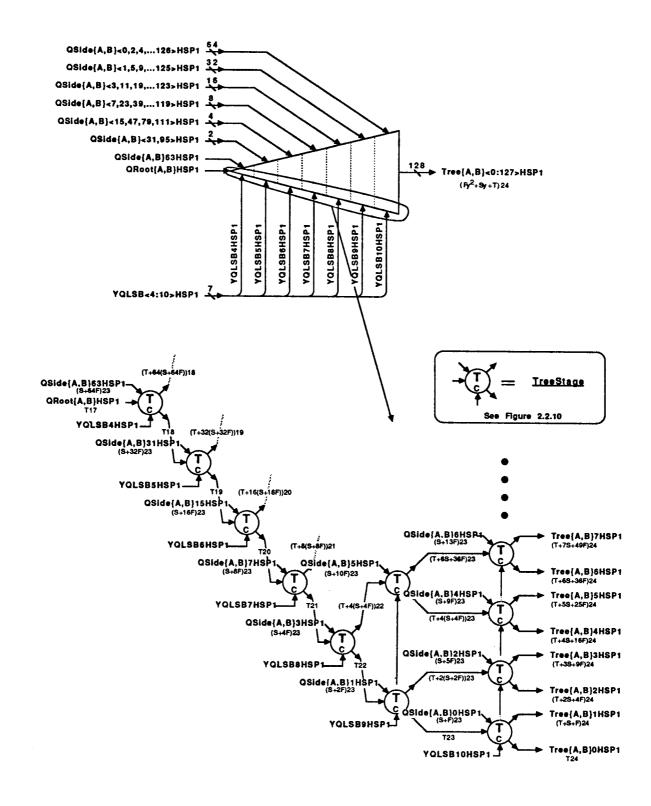

- Quadratic Expression Evaluator. In Pxpl5, we are replacing the linear expression tree on Pxpl4 with a quadratic expression evaluator tree that produces the function Ax+By+C+Dx<sup>2</sup>+Exy+Fy<sup>2</sup> simultaneously at each pixel. We expect that quadratic expressions will be especially useful in rendering CSG objects and for direct rendering of quadratic patches and objects composed of conic sections.

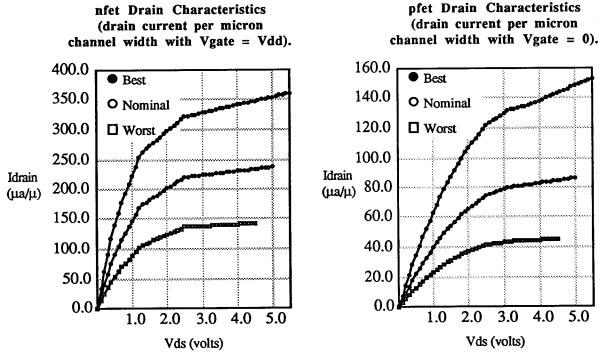

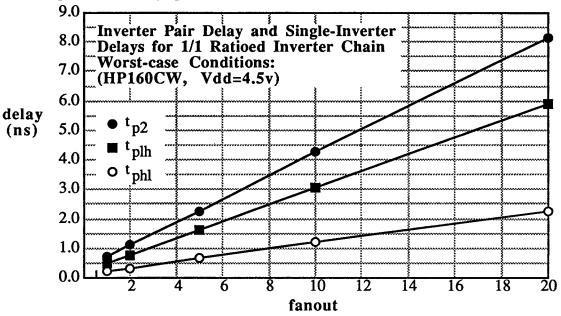

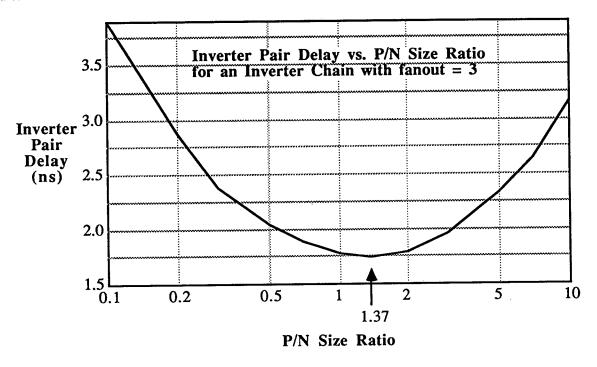

- Faster, Denser Chips. Performance can readily be improved by using better semiconductor technology. The Enhanced Memory Chips (EMC's) for Pxpl5 use 1.25µ CMOS technology and are specified to run at 40 MHz for a 4-5x improvement in speed. Algorithm developers who use Pxpl4 are constantly frustrated by the relatively small amount (72 bits) of local memory at each pixel processor, so we are providing 256 bits of memory at each pixel on the Pxpl5 EMC.

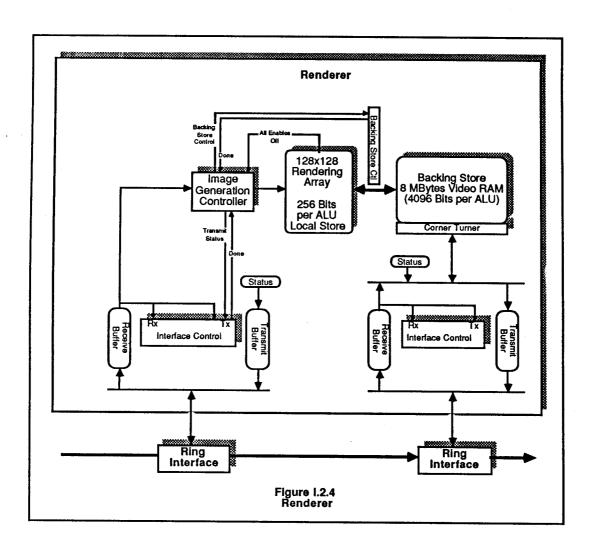

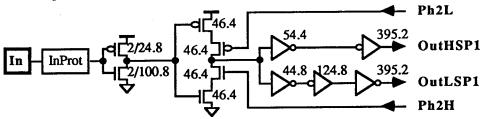

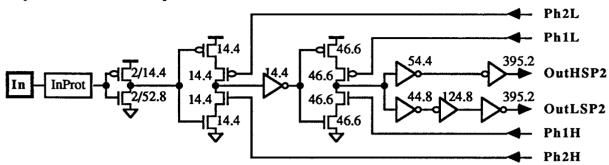

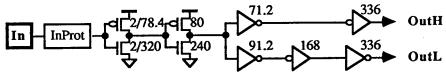

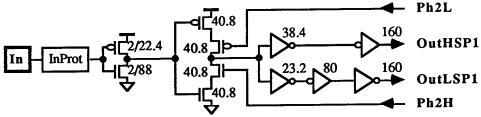

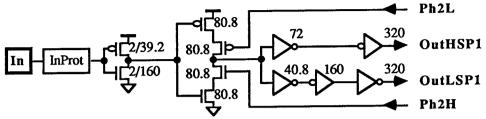

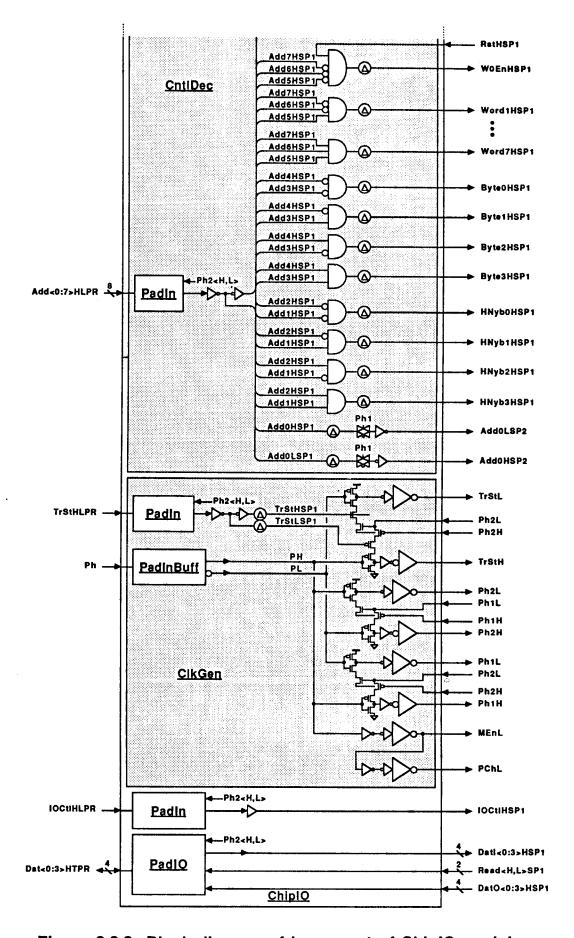

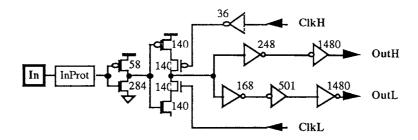

Figure 3: Simplified block diagram of Pxpl5 Renderer.

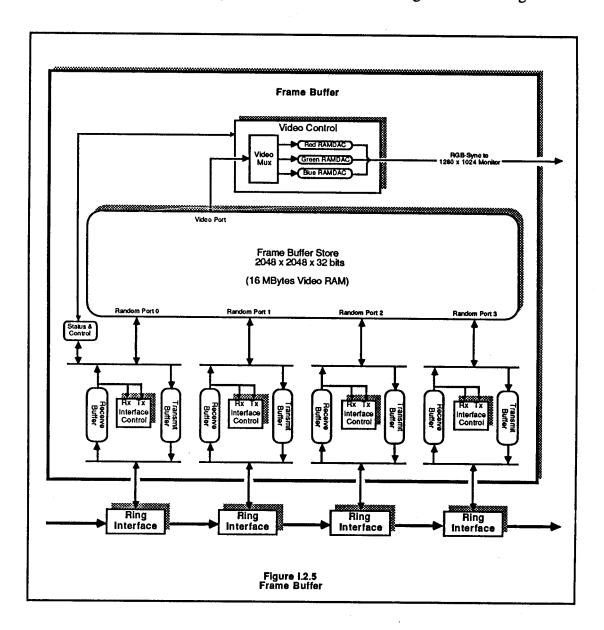

### Frame Buffer

The Frame Buffer is built in a fairly conventional way using Video RAM's. The Video port of this RAM array sends pixel three (R-G-B) color values (8 bits each) and a user-defined fourth value through a color lookup table to video DAC's. The video circuitry is sufficiently flexible to handle a variety of display hardware, and it provides a "gen-lock" input to support video recorders and cameras. The Frame Buffer is accessed through four Ring Nodes, to provide an aggregate bandwidth of 80 MWords/sec into the buffer. For real-time screen update (up to 60 Hz), the Video RAM random I/O port is connected to these Ring Nodes in such a way that it appears four-ported, i.e., messages arriving at any of the four Nodes can go to any memory location.

#### **Host Interface**

In its first implementation, Pxpl5 will be hosted by a UNIX workstation. Communications to the Host will be supported by a DEC DR11-style DMA interface at the Host end and the Host Interface at Pxpl5 end. The Host Interface simply executes the protocol expected by a DMA device, and allows blocks of memory data to be passed between any Device on the Ring and the Host.

# Part I Chapter 2

# HARDWARE OVERVIEW

In this chapter, we outline the architecture for Pixel-planes 5, which we believe satisfies the objectives given in Chapter I.1, with the exception of the unrealistic power requirement of that chapter.

Figure I.2.1 shows Pxpl5 as a set of devices plugged into the ports of a communications network called the *Ring*.

### I.2.1. THE RING

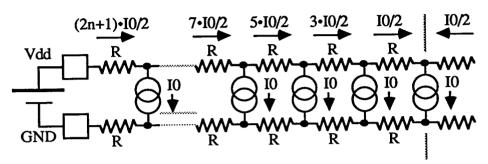

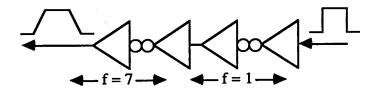

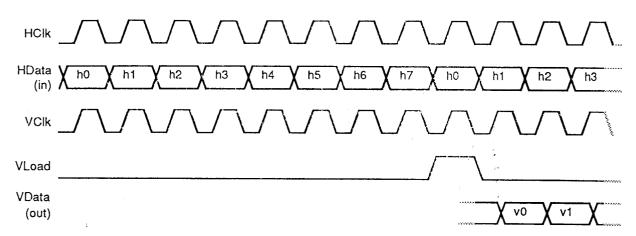

The ring is a 160 MHz ring network which distributes data from port to port in a circular fashion. The ring can be thought of as a collection of cars, which move one stop clockwise every 6.25 nsec. Optimally, a port can place data in every eighth car of the Ring, giving a maximum transmission rate from any one port of 20 MWords / sec. Transmissions from different ports may interleave, as shown in figure I.2.2.

The ring has a 32-bit address space. The low 25 bits give a word address on any selected ring device. The high order 7 bits specify one of 128 ring nodes.

A device on the ring sends a packet of data to another device by writing a 32-bit destination address into the transmit buffer of its ring interface, followed by a 32-bit source address, then the data. The high order 6 bits of the destination address indicate a ring node; the low order 25 bits give a word address on the device connected to that node. The low order 25 bits of the source address optionally indicate a word address on the device sending the packet.

When the system is powered up, the Host reads a "device id" register from each ring node to determine the ring configuration. Application programs use this information to take best advantage of the devices available on the ring.

## I.2.2 RING DEVICES

The following sub-sections describe the ring devices and their interfaces to the ring.

# I.2.2—1 Host Interface (HIF)

The Host Interface allows the host workstation to broadcast and receive packets on the ring. This link is supported by a DRV-11WA DMA interface card in the host. The Host Interface also initializes the ring upon system power-up.

When a host application wishes to send a packet to a device on the ring, it sends the packet to the Host Interface via the DR-11 DMA interface. The Host Interface then places the packet on the ring, where it is routed to the intended device.

When the Host wishes to read data from a ring device, it must first send a packet to that device as outlined above. That packet instructs the device to return a packet encapsulating the requested data. The Host sets up the DR-11 to transfer the return packet back to the Host when it arrives at the Host Interface.

Devices can send asynchronous packets to the HIF which cause the HIF to interrupt the Host. This facility is intended for reporting errors and debug packets. The HIF also reports ring timeout and hardware errors to the Host.

# I.2.2—2 Graphics Processor (GP)

The Graphics Processor (GP) is intended to be the local manager in the Pixel-planes 5 system. It is based on the 10 MHz Weitek XL chip set, a Harvard processor optimized for fast floating point calculation. The GP is capable of 10 million multiply-accumulates per second. Although the GP is considered the overall system supervisor, it has no special privileges on the Ring.

When a packet arrives at the GP, its Interface Controller looks at the destination address of the packet and routes the packet to the appropriate location on the GP. Packet types received by the GP include:

<u>Data Write:</u> Write to data store. The packet body is written into Data Store at

an address given in the low 25 bits of the packet destination address. The processor is then interrupted, and may examine a registers to determine the packet length, it's source device, and

where it was written.

<u>Data Read:</u> Read from data store. The packet body contains two addresses

source and dest, and an integer count. Count words are read from data store address source and transmitted as a packet on the

ring to address dest.

<u>Code Write:</u> Write to code store. The processor is stopped, then the packet

body is written into Code Store at at an address given in the low

25 bits of the packet destination address.

<u>Code Read:</u> Read from code store. The packet body contains two addresses

source and dest, and an integer count. The processor is stopped, then Count words are read from code store address source and transmitted as a packet on the ring to address dest

source and transmitted as a packet on the ring to address dest.

Stop: The processor is stopped.

<u>Start:</u> The processor is reset and begins execution at location zero.

Status Read: Read the GP device id and status. The packet body contains an

addressdest. The device id and status are transmitted in a two

word packet to address dest.

The GP can send packets out of its data store by writing the source address, destination address, and length of the packet into control registers of the interface controller. The controller interrupts the GP upon completion of the packet transmission.

## I.2.2—3 Graphics Accelerators

The Graphics Accelerators (GA's) are copies of the GP with smaller code and data stores. Each GA has 4 MBytes of data store and 512 KBytes of code store.

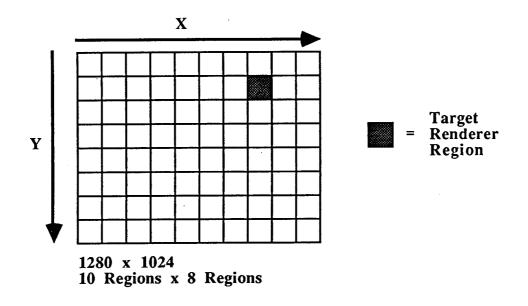

In triangle rendering applications, the GA's are used in parallel to transform geometric primitives into linear expression representations, and to sort those transformed primitives into bins corresponding to regions of the frame being rendered. The GA's may also be used to apply texture table lookups to images.

A high end Pixel-planes 5 system will have 32 GA's on the ring. At 32 K $\Delta$ 's/sec per GA, this will give the target performance of one million  $\Delta$ 's/sec.

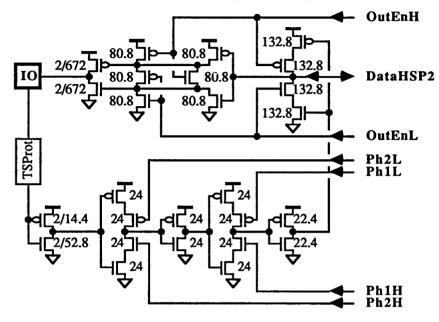

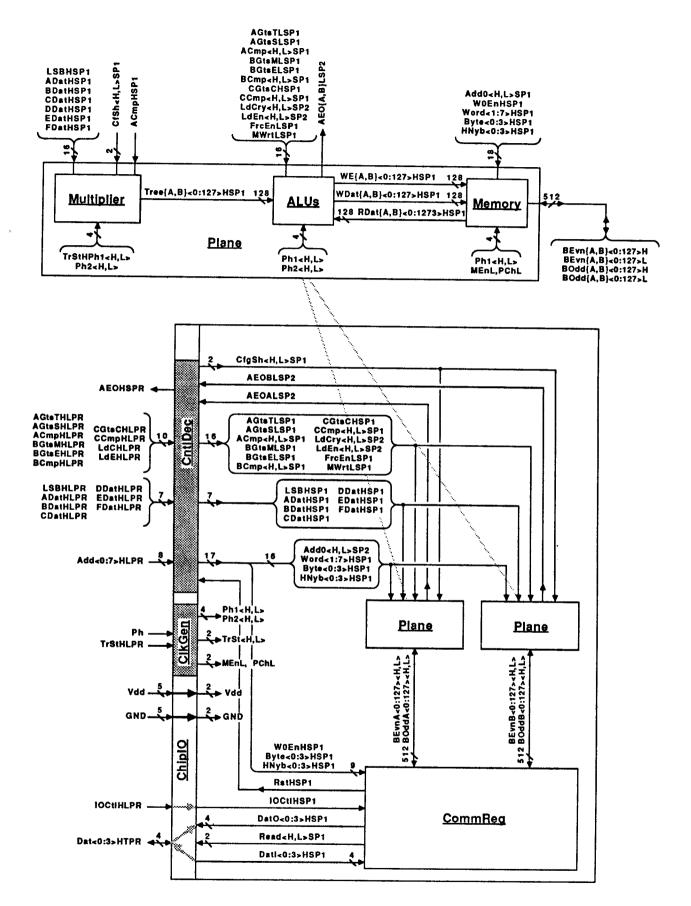

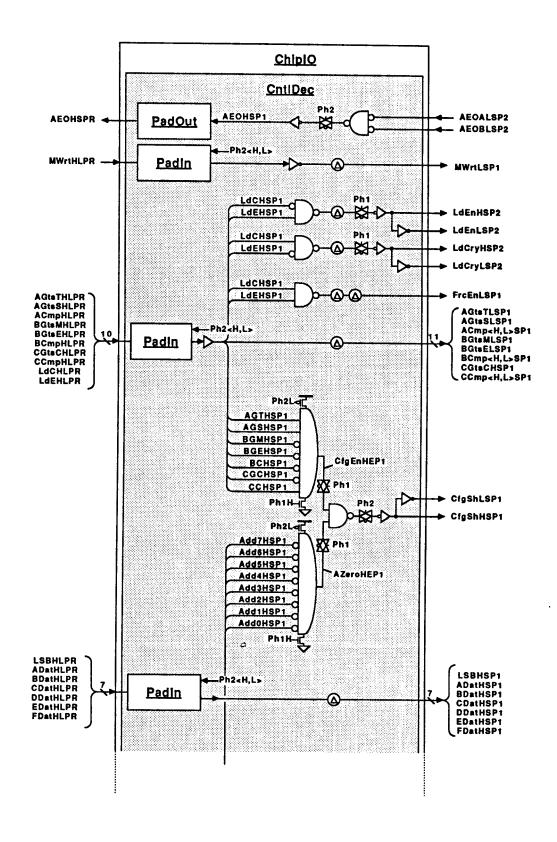

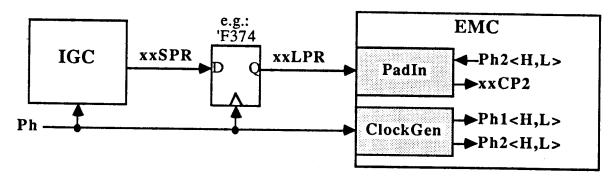

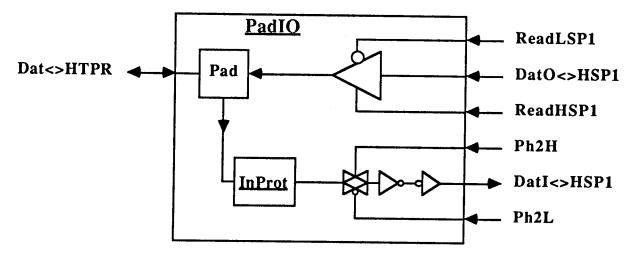

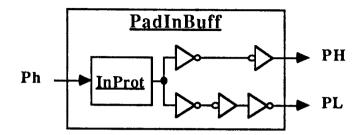

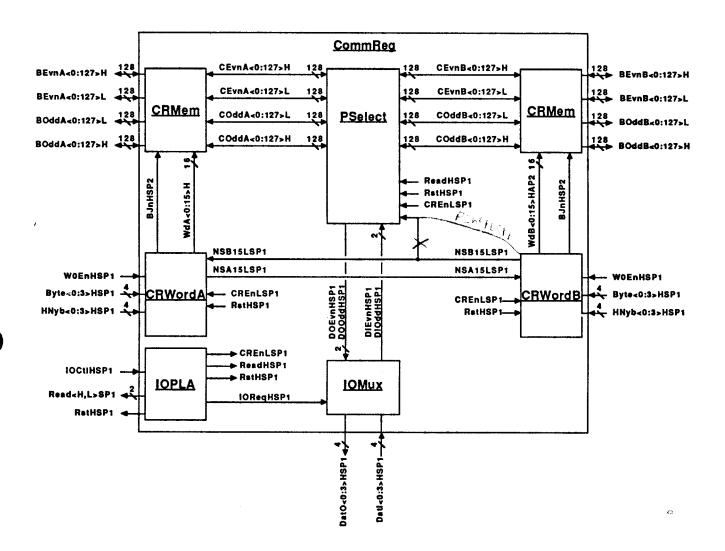

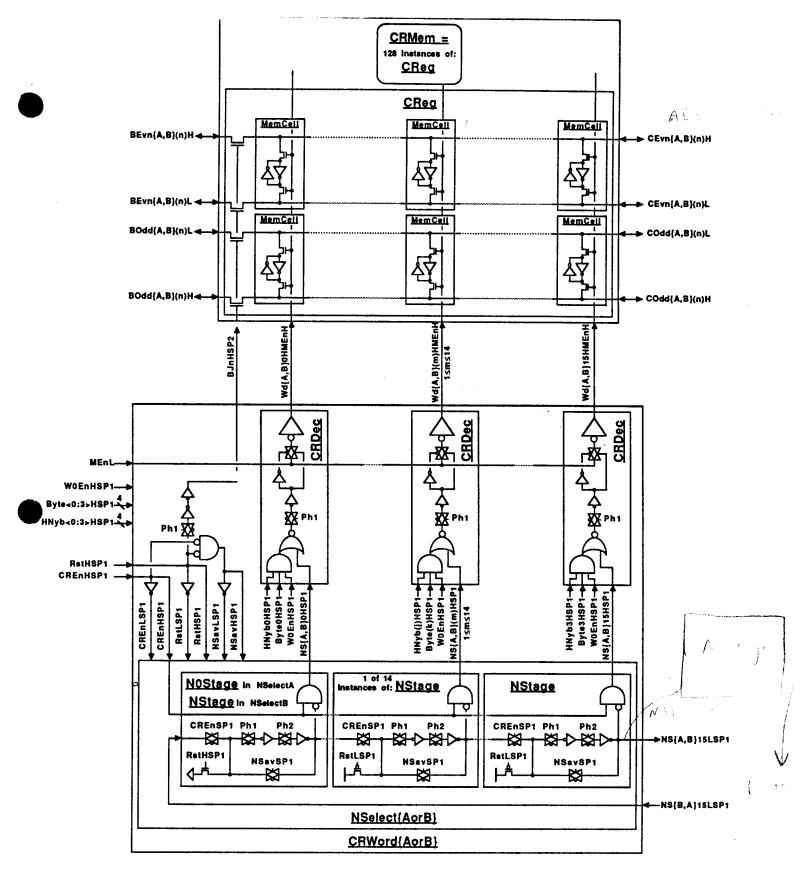

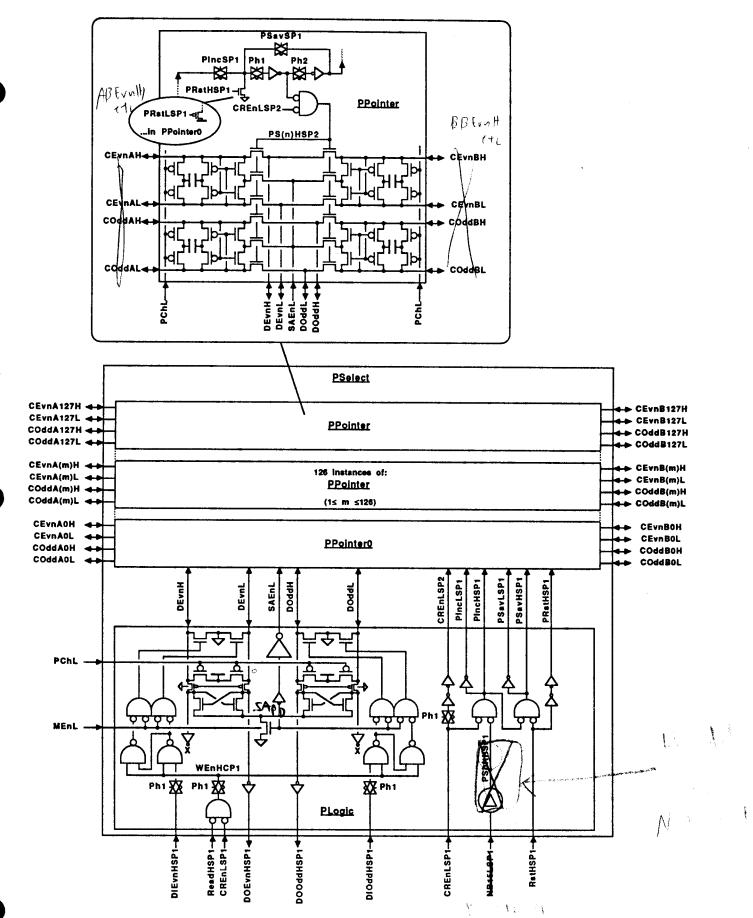

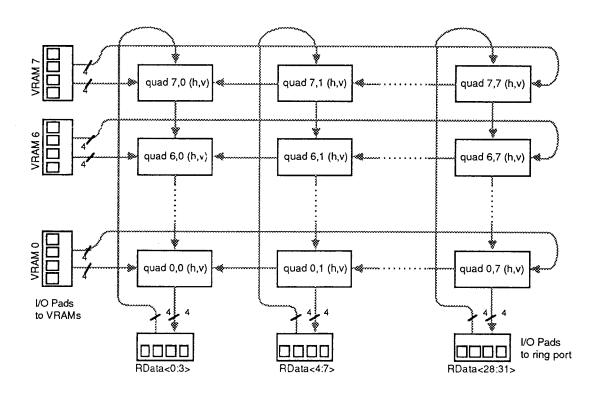

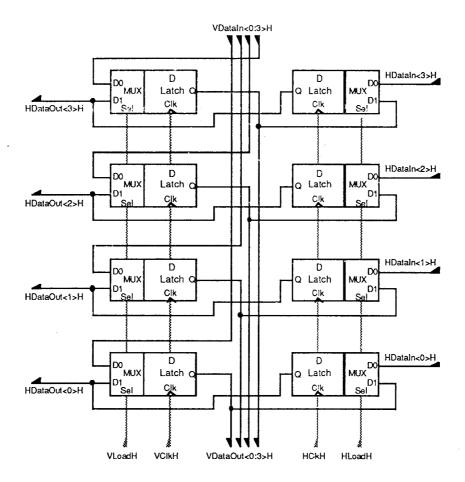

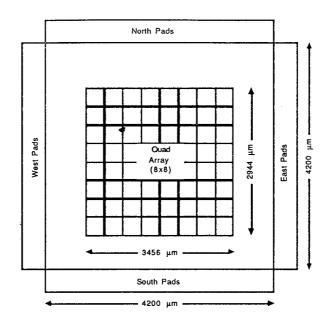

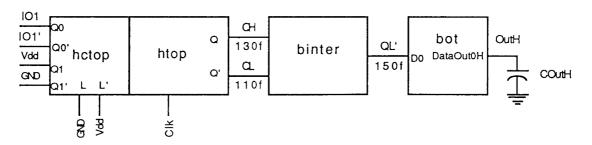

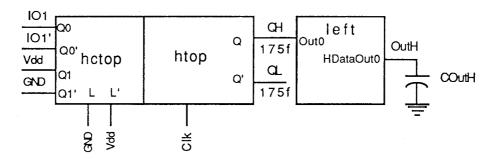

#### I.2.2—4 Renderers

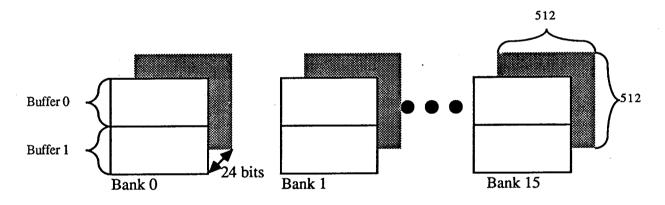

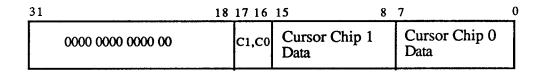

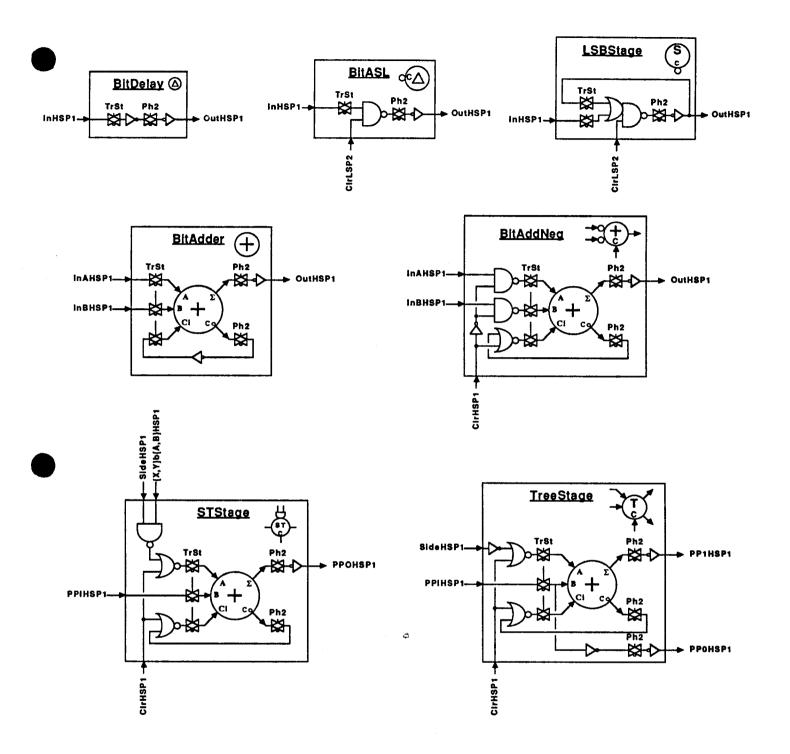

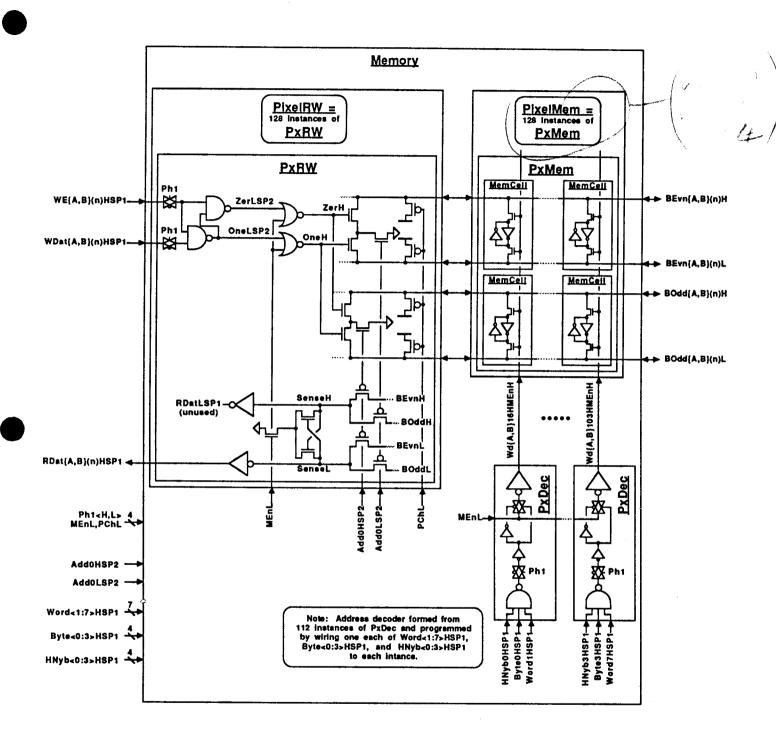

A Renderer is a 128 x 128 array of 40 MHz bit serial ALU's, each with 256 bits of tightly coupled local data store. A quadratic expression evaluator (the Tree) delivers bi-quadratic expressions in x and y simultaneously to each ALU. The ALU's and the Tree and are

controlled in SIMD fashion by the Image Generation Controller (IGC).

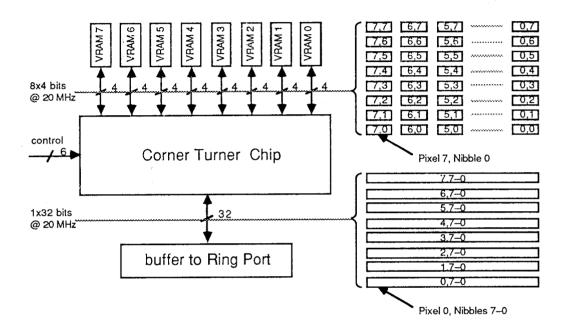

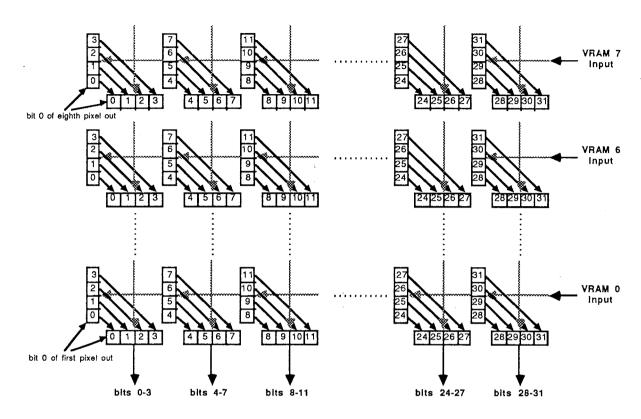

The local store of each ALU is supplemented with 4096 bits of loosely coupled backing store, organized as 128 32-bit registers per ALU. The IGC controls the parallel loads and stores of 32-bit words from backing store to local store. A single backing store operation, dispatched by the IGC, loads or stores the low order 32 bits of local store to a specified backing store register array. After dispatching a backing store operation, the IGC can continue to execute ALU commands as the backing store operation proceeds concurrently. It can wait for completion of the backing store operation by monitoring a done flag from the BSC. One backing store operation will take slightly more than 4096 image generation cycles, about 100 µsec.

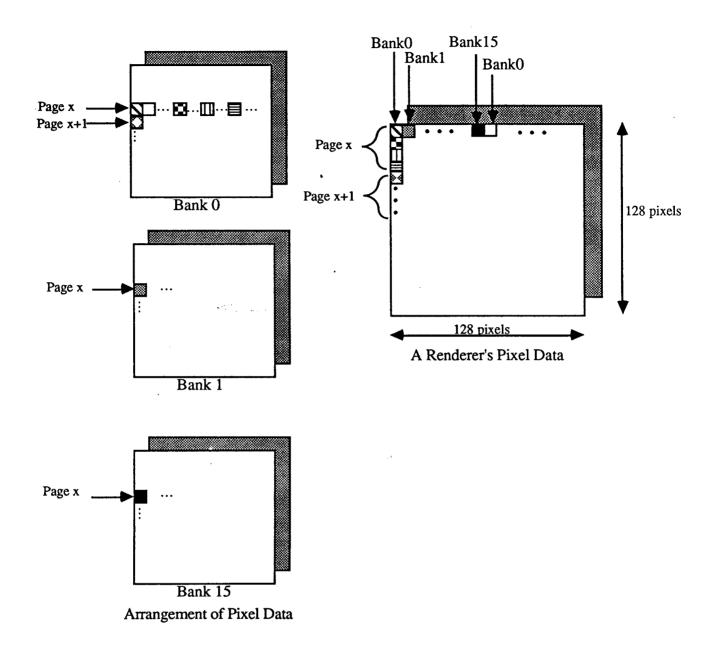

A Renderer has two ports onto the ring. The first port receives commands for the IGC; the second is used to read and write the backing store. From the ring, the backing store appears as 128 separate 128 x 128 arrays of 32-bit values. In a typical rendering application, these arrays will be transferred over the ring to the Frame Buffer to become pixel regions.

Packet types received by a Renderer's IGC port include:

Command Buffer Write:

The packet body is placed in the IGC command buffer.

Status Read:

Read the IGC port id and status. The packet body contains an address *dest*. The port id and status are transmitted over the ring to address *dest*.

Packet types received by a Renderer's backing store port include:

**Backing Store Write:**

Write to backing store. The packet body is written into Backing Store at an address given by the low order bits of the packet destination address. This address specifies one of the 128 backing store register arrays.

**Backing Store Read:**

Read from backing store. The packet body contains two addresses *source* and *dest*. A register array given by *source* is read from backing store and transmitted as a packet on the ring to address *dest* (typically a Frame Buffer address).

Status Read:

Read the backing store port id and status. The packet body contains an address *dest*. The port id and status are transmitted over the ring to address *dest*.

## I.2.2—5 Frame Buffers

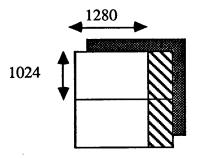

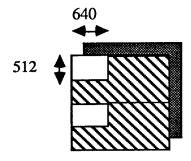

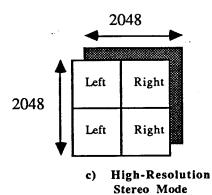

A Frame Buffer is a 2048 x 2048 x 32 bit memory array, with four ports on the ring and a video port out to a 1280 x 1024 monitor. The four ring ports allow up to four ring devices to simultaneously read or write 20 MWords / sec into the Frame Buffer Store. A Pixel-planes 5 system will support multiple Frame Buffers; two Frame Buffers will support stereo imaging nicely.

From the ring, a Frame Buffer Store is organized as a 32 x 16 array of 64 x 128 x 32 bit regions. These regions are the same size as the ALU arrays in the Renderers, so a Renderer register array can be copied directly to or from a Frame Buffer region over the ring.

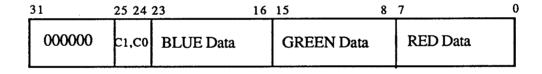

Bytes 0, 1, and 2 of the Frame Buffer are denoted the Red, Green, and Blue bytes, respectively. These three bytes are streamed from a window in the Frame Buffer Store into the video RAMDAC's, which perform the red, green, and blue color lookups and drive the video output.

The size and location of the display window within the Frame Buffer is controlled by a control register written from the ring. The window can be one of three sizes:  $1280 \times 1024$ ,  $640 \times 512$ , or  $320 \times 256$ . Its location within the Frame Buffer, also determined by a control register, must be aligned on region boundaries.

The RAMDAC's are 12 bit lookup tables driving 12 bit DAC's. The three video bytes can be mapped into the video RAMDAC's in three different ways, depending on the lookup mode:

RGB:

The red, green, and blue bytes are streamed into the red, green, and blue RAMDAC's, respectively. The low order nibbles of the

RAMDAC inputs are set to zero.

Mono8:

The red byte is streamed into all three RAMDAC's for 8 bit monochrome. The low order nibbles of the RAMDAC inputs are

set to zero.

Mono12:

The red byte and the low order nibble of the green byte are streamed together into all three RAMDAC's for 12 bit

monochrome. The green bits are the least significant.

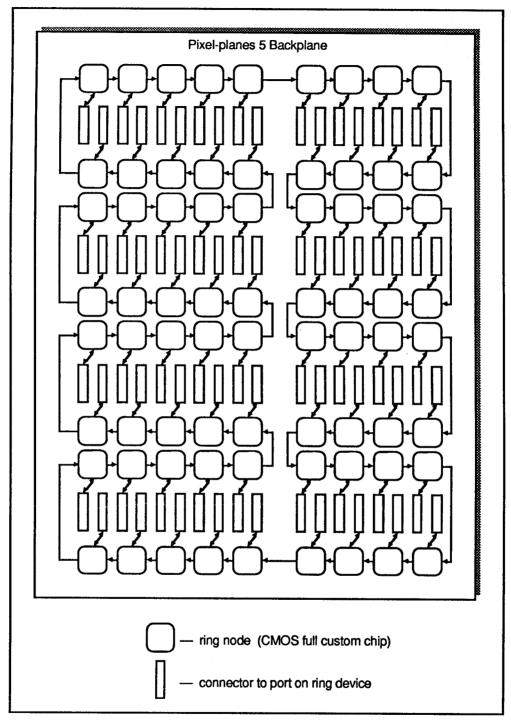

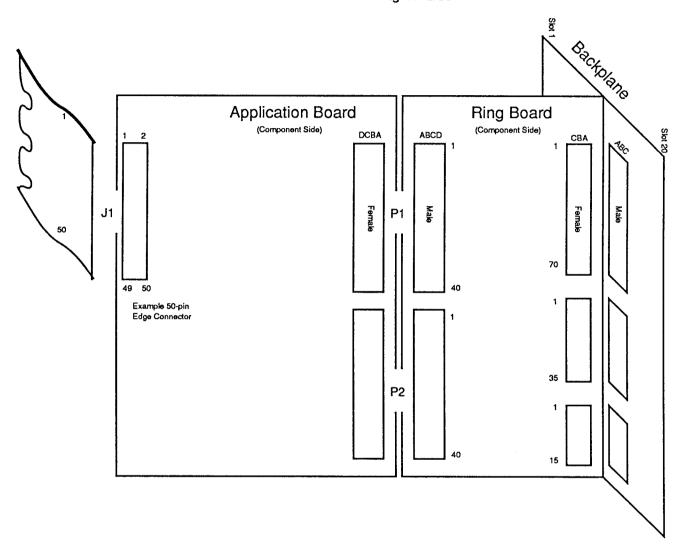

# I.2.3 PACKAGING

The backplane has 18 slots, 4 ring ports to a slot. Each ring node is implemented in a custom CMOS part on the backplane, connected into a ring as shown in figure 1.2.6. The ring nodes (squares in the diagram) are connected to the rectangular connectors to ring devices. The connectors are arranged in 18 slots of four connectors. The 18 slot limit is imposed on us by a maximum backplane size; the ring node parts themselves will support a ring with 128 nodes.

A ring device may be built on a quarter, half, three-quarter, or full height board. A full height device will occupy a full slot, and may have up to four ring ports. A quarter height device will occupy one fourth of a slot, and may have only one ring port. The half and three-quarter height devices work similarly. For mechanical integrity, ring devices of less than full height must be bolted together to form a full height board before being plugged into the backplane.

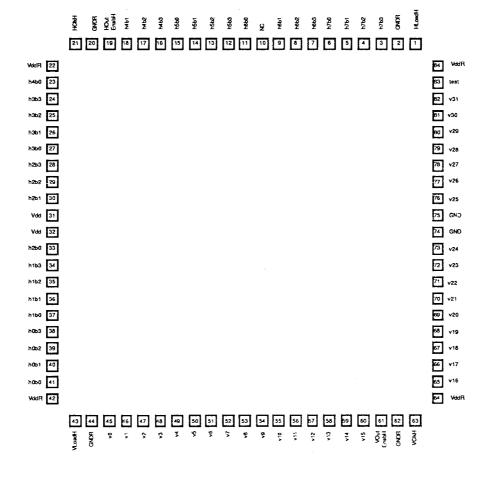

Figure 1.2.6 Backplane

The Host Interface occupies a quarter height board; The GP occupies a half height board. Together, these two devices occupy one slot. A Graphics Accelerator is implemented on a

quarter-height board, a Renderer occupies one half-height board, and the Frame Buffers each occupy a full-height board.

A full blown system might have the following ring devices:

| Host Interface / GP | 1 slot   |

|---------------------|----------|

| 32 GA's             | 8 slots  |

| 16 Renderers        | 8 slots  |

| 1 Frame Buffer      | 1 slots  |

| total:              | 18 slots |

Other organizations are certainly possible. For example, an additional Frame Buffer could be added at the expense of two Renderers for stereo imaging.

# PART II Power, Packaging, & Cooling

- 1. Ring Network

- 2. Backplane

- 3. Power Supplies4. Cabinet Mechanicals

# II.1.3. RING ARCHITECTURE

This section describes the Pxpl5 ring network as follows:

| Subsection 1 | Describes the ring as a "multi-ring." |

|--------------|---------------------------------------|

| Subsection 2 | Packet format and ring addresses.     |

| Subsection 3 | Error packet format & Board ID's.     |

| Subsection 4 | Hardware interface to the ring.       |

| Subsection 5 | Port connector pinout.                |

# II.1.3—1 The Ring

The Pxpl5 ring is an 8-way multi-ring with a 160 MHz control path and 8 32-bit channels time-multiplexed onto a 160 MHz 32-bit data path. All device interfaces to the ring are synchronous. The ring's behavior is defined in the previous section on the multi-ring.

A device's interface to the ring is called a *port*. A device may have more than one port, depending on its board height and needs. A single height board has one port, a double height board has two ports, and one can imagine schemes with sandwiched boards allowing devices with more than two ports.

One device sends data to another by clocking a *packet* into the *transmit interface* of one of its ports. The packet format includes the destination port address of the packet, allowing the ring to transfer the packet to the *receive interface* of the intended port on the receiving device.

# II.1.3—2 Packet Format and Ring Addresses

A ring packet consists of a 32-bit destination address, then zero or more 32-bit data words.

Example 4 word Ring

| i | Packet:             |

|---|---------------------|

|   | Destination Address |

|   | Data Word 0         |

|   | Data Word 1         |

|   | Data Word 2         |

|   | Data Word 3         |

Ring addresses have two fields: a 7-bit node address and a 25-bit word address. Thus the ring supports up to 128 nodes, each with a 32 Mword address space.

#### Ring Address:

| 31  | 25    | 24          | 0    |

|-----|-------|-------------|------|

| No  | de    | Word Addres | s on |

| Add | dress | Device      |      |

| 1   |       |             |      |

## II.1.3—3 Error Packets and Board ID's

This sub-section specifies the format of an *error packet* to be sent in the event of a low level system error. Errors falling into this category might include

- Receiver buffer overflow (message too long).

- IGC Hung on a renderer.

- Invalid Code or Data Address (Bus Error) on a GP.

This error handling scheme is not to be invoked upon high level errors such as an overflowing bin in the Rendering Control System, or an invalid PPHIGS command detected at a GP.

When a device detects an error, it should send a packet to the Host Interface device, which always resides at ring address zero. The Host Interface and host software should recognized packets sent to address zero as error packets.

The following error packet format should be used:

#### Error Packet:

| Destination Address (hex 0000 0000) |

|-------------------------------------|

| Board ID Word                       |

| Board Status Word                   |

The low-order byte of the Board ID word is an eight bit board serial number. The high 24 bits of the Board ID word are undefined. Each application board is assigned a unique serial number when it arrives from fabrication and assembly. The serial numbers are stored in a system file for access by system software.

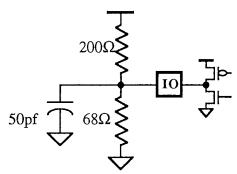

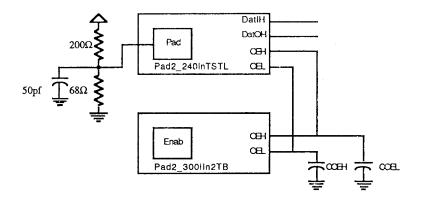

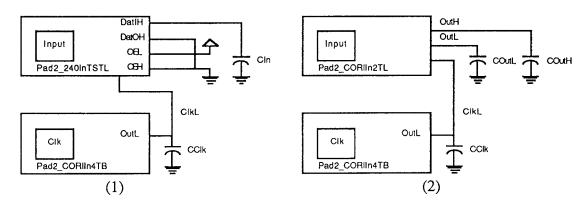

#### II.1.3—4 Ring Port Specification

A double-height board has two independent ring ports. The signals for one port are carried from the ring board to the application board via two 160-pin DIN connectors, one per port. These signals can be broken into three groups: miscellaneous, receive, and transmit signals.

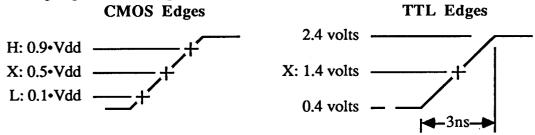

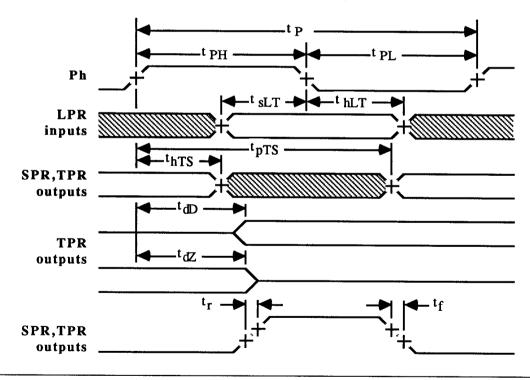

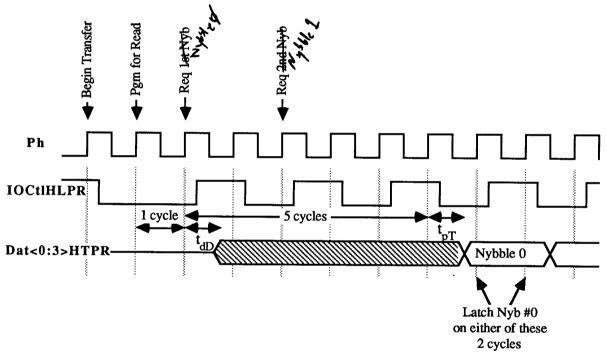

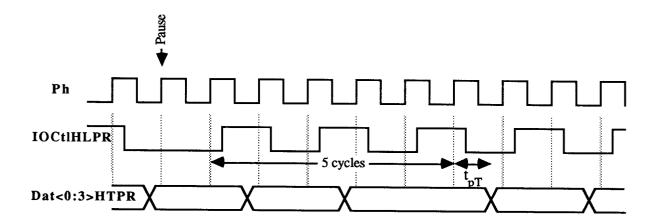

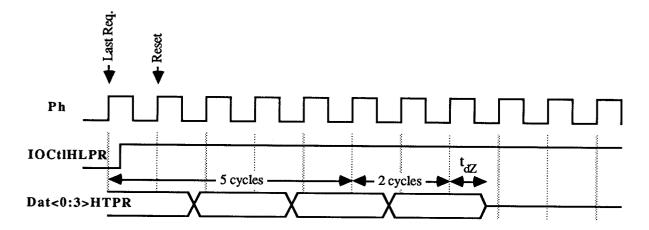

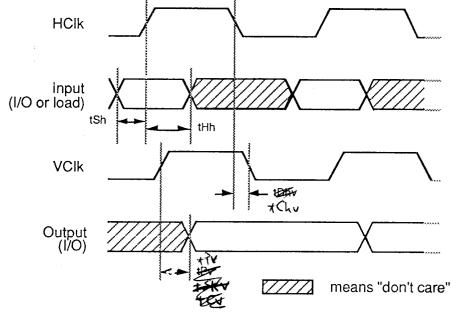

Signal Timing

All ring interface signals are synchronous with respect to the 20 MHz clock Ring20ClkH. The two numbers following device-originating signals are the setup and hold times in nsec with respect to Ring20ClkH. The two numbers following ring-originating signals are the min and max prop delays in nsec for those signals with respect to Ring20ClkH. Note that these times are with respect to an ECL clock signal, and must be adjusted to account for translating the clock to TTL levels.

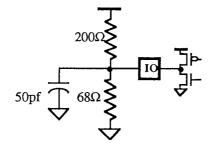

Signal Termination

Application boards may be mounted on 15" extender boards for debugging. To this end, the application board should terminate all TTL signals received from the ring with  $100\Omega$ terminators (160/240 Thevenin Equivalent). The ring board will do likewise for all TTL signals it receives from the application board.

The application board should route the ECL clocks on  $50\Omega$  traces and terminate them to VTT through  $50\Omega$ .

Signal Polarity

All ring signals are active high unless suffixed with 'L', in which case they are active low.

#### II.1.3—4.1 Miscellaneous Signals

| Ring40ClkH<br>Ring40ClkL . |          | 40 MHz differential ECL clock, provided for 40 MHz devices such as the Renderer.                                                                                                   |

|----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ring20ClkH<br>Ring20ClkL . |          | 20 MHz differential ECL clock, the basis for all ring interface timing. Ring20ClkH is phase-aligned with Ring40ClkH.                                                               |

| Reset                      | [5:14]   | Asserted by ring to reset devices. Will be asserted for at least 2 $\mu$ sec. After the ring de-asserts Reset, ring devices should be in an idle state, ready to receive a packet. |

| ResetGenL                  | [Async]  | The Host Interface asserts this signal on node0 for at least 2 $\mu$ sec to boot the ring and all attached devices. All other devices leave this signal unconnected.               |

| ResetEnabL .               | [Static] | The Host Interface ties this signal to GND on node0; all other devices leave this signal unconnected. (ResetGenL and ResetEnabL are ignored on node1.)                             |

| OccupiedL                  | [Static] | All devices tie this signal to GND.                                                                                                                                                |

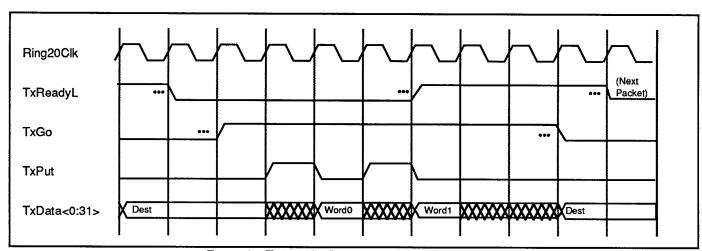

# II.1.3—4.2 Transmit Signals

TxPut

TxData<0:31>

TxReadyL [28:4] The transmitting device asserts this signal when it is ready to transmit a packet, and de-asserts it on or after the last data word of the packet.

If the intended receiver device is hung (never ready for a packet), the ring will never assert TxGo to the transmitting device. In this case, the transmitting device can report the problem by deasserting TxReady to abort the failed transmission, then sending an error packet to the Host Interface in the usual fashion.

TxGo [5:22] The ring asserts this signal when it has acquired the receiver and a channel for data transmission. The device may then clock in data with the TxPut signal.

The ring deasserts TxGo no sooner than three cycles after the device deasserts TxReady. The device must not reassert TxReady (for a new packet) until the cycle after TxGo is deasserted.

[15:0] The device clocks the rest of the packet across the interface by asserting this signal one cycle before each data word. TxPut is a level sensitive signal, and may be asserted on consecutive cycles for consecutive data words. TxPut must not be asserted after TxReady has been deasserted for a packet.

[9:0] Transmit data asserted by device—consists of packet destination address and data words.

The device places the packet destination address on TxData one or more cycles before asserting TxReady, and leaves it there until the ring asserts TxGo.

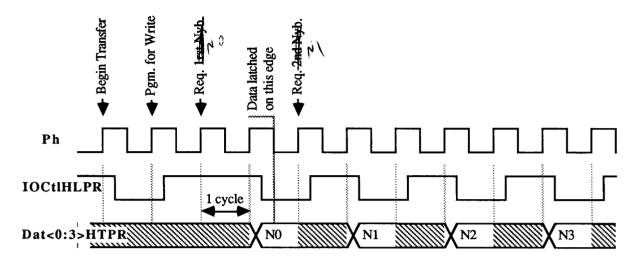

Example Transmit Sequence — 2 word packet

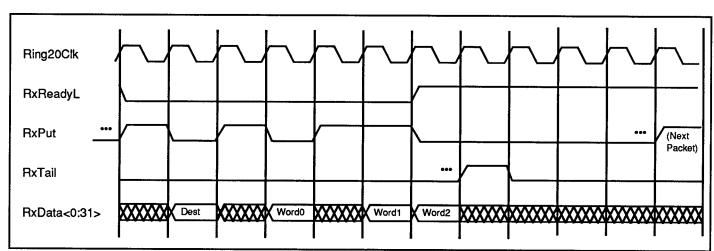

# II.1.3—4.3 Receive Signals

| RxReadyL     | [28:4] | The device asserts this signal to indicate that it can receive a "maximum length" packet. This length varies from device to device.                                            |

|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |        | RxReady is not monitored by the ring after the node begins receiving a packet. Typically this signal is a mousetrapped HalfFull flag from a IDT FIFO part.                     |

| RxPut        | [2:7]  | The ring asserts this signal one cycle before the destination address and each data word. The ring may deassert RxPut on any cycle in the receive sequence to skip that cycle. |

| RxTail       | [2:7]  | The ring asserts RxTail to indicate the end of the packet. It may be asserted as soon as the cycle after the last data word.                                                   |

|              |        | The ring will assert RxPut for the next packet no sooner than 4 cycles after RxTail.                                                                                           |

| RxData<0:31> | [2:7]  | Receive data asserted by ring—consists of packet destination address and data words.                                                                                           |

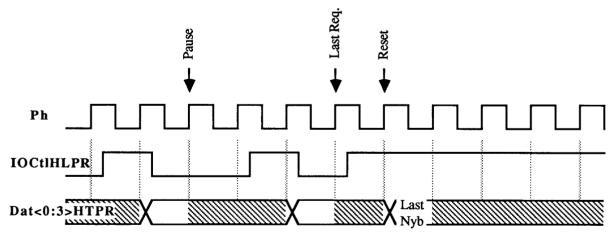

Example Receive Sequence — 3 word packet

# II.1.3—5 Ring Port Connector

The following pinout applies to the connection to both ring nodes, on connectors P1 and P2 for node0 and node1, respectively.

|    | A          | В        | С          | D         |

|----|------------|----------|------------|-----------|

| 1  | RxData0    | VCC      | RxData1    | GND       |

| 2  | VCC        | RxData2  | GND        | RxData3   |

| 3  | RxData4    | VCC      | RxData5    | GND       |

| 4  | VCC        | RxData6  | GND        | RxData7   |

| 5  | RxData8    | VCC      | RxData9    | GND       |

| 6  | VCC        | RxData10 | GND        | RxData11  |

| 7  | RxData12   | VCC      | RxData13   | GND       |

| 8  | VCC        | RxData14 | GND        | RxData15  |

| 9  | RxData16   | VCC      | RxData17   | GND       |

| 10 | VCC        | RxData18 | GND        | RxData19  |

| 11 | RxData20   | VCC      | RxData21   | GND       |

| 12 | VCC        | RxData22 | GND        | RxData23  |

| 13 | RxData24   | VCC      | RxData25   | GND       |

| 14 | VCC        | RxData26 | GND        | RxData27  |

| 15 | RxData28   | VCC      | RxData29   | GND       |

| 16 | VCC        | RxData30 | GND        | RxData31  |

| 17 | TxData0    | VCC      | TxData1    | GND       |

| 18 | VCC        | TxData2  | GND        | TxData3   |

| 19 | TxData4    | VCC      | TxData5    | GND       |

| 20 | VCC        | TxData6  | GND        | TxData7   |

| 21 | TxData8    | VCC      | TxData9    | GND       |

| 22 | VCC        | TxData10 | GND        | TxData11  |

| 23 | TxData12   | VCC      | TxData13   | GND       |

| 24 | VCC        | TxData14 | GND        | TxData15  |

| 25 | TxData16   | VCC      | TxData17   | GND       |

| 26 | VCC        | TxData18 | GND        | TxData19  |

| 27 | TxData20   | VCC      | TxData21   | GND       |

| 28 | VCC        | TxData22 | GND        | TxData23  |

| 29 | TxData24   | VCC      | TxData25   | GND       |

| 30 | VCC        | TxData26 | GND        | TxData27  |

| 31 | TxData28   | VCC      | TxData29   | GND       |

| 32 | VCC        | TxData30 | GND        | TxData31  |

| 33 | RxPut      | VCC      | RxTail     | GND       |

| 34 | VCC        | RxReadyL | GND        | TxPut     |

| 35 | TxReadyL   | VCC      | TxGo       | GND       |

| 36 | VCC        | Reset    | OccupiedL  | ResetGenL |

| 37 | ResetEnabL | VTT      | VEE        | VEE       |

| 38 | VIT        | VIT      | VEE        | VEE       |

| 39 | Ring20ClkH | GND      | Ring40ClkH | GND       |

| 40 | Ring20ClkL | GND      | Ring40ClkL | GND       |

# **Pixel-Planes 5 Board and Connector Conventions**

tg 7/18/89

# PART III Application Boards

- 1. Host Interface Board

- 2. Graphics Processor Board

- 3. Graphics Accelerator Board

- 4. Renderer Board

- 5. Frame Buffer Board

# Part III Chapter 1

# HOST INTERFACE

#### 1.1 Introduction

The Host Interface provides a link between the Pixel-planes5 host, a Sun-4, and the devices attached to the ring network, such as renderer boards and graphics processor boards. The Host Interface (HIF) passes data to and from the host via a VME prototype board plugged into the Sun. The HIF and host driver are responsible for booting the ring network. Information concerning the VMEbus may be obtained from The VMEbus Specification.

## 1.2 Implementation Overview

#### 1.2.1 Division of Function

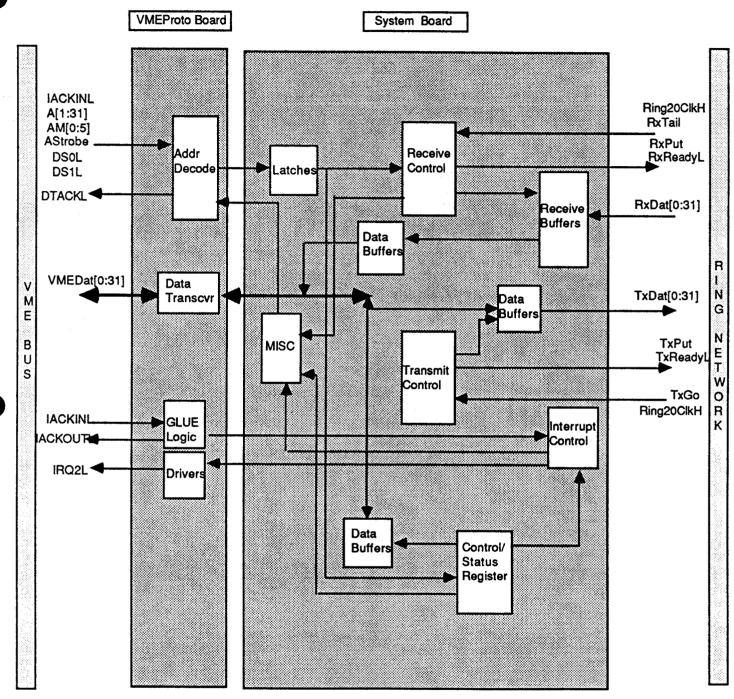

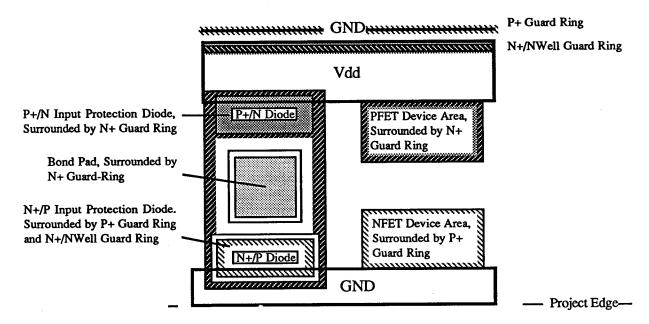

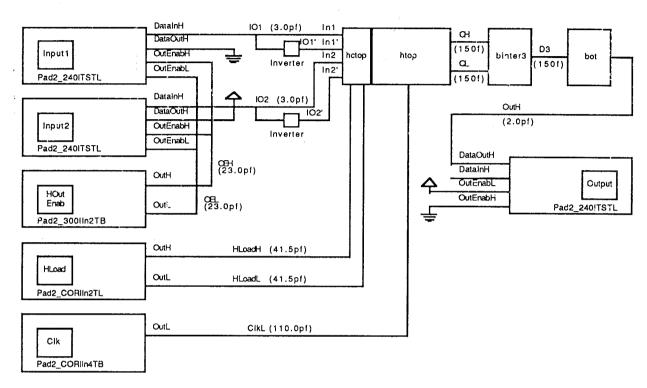

The Host Interface for PXPL5 is implemented as two physically separate circuit boards. The VME prototype board contains buffers for the VMEbus signals and decode logic to identify VMEbus cycles which are intended for the Host Interface. The VME board also contains the data transceivers and the logic to generate certain VMEbus signals when the other board is not operational. The remainder of the Host Interface logic which includes data transmission control, data receipt control, register control, and interrupt control, resides on a second board, referred to as the system board. The system board is connected to the VME prototype board via two ribbon cables and is also connected to a PXPL5 ring network board. The following signals are transferred between the protoboard and the system board. Figure 1 is a block diagram of the two boards which comprise the Host Interface.

#### D[0:31]

These signals comprise the 32-bit bidirectional data bus between the protoboard and the system board. Bit 0 is least significant and bit 31 is most significant.

## WrPktCycleUL

This signal is low-active and is generated on the protoboard. When active, the current VME cycle is a "write packet" cycle.

## RdPktCycleUL

This signal is low-active and is generated on the protoboard. When active, the current VME cycle requests the contents of a receive buffer.

# WrCSRCycleUL

This signal is low-active and is generated on the protoboard. When active, the current VME cycle is for writing bits 0-2 of the *Control and Status Register*.

# RdCSRCycleUL

This signal is low-active and is generated on the protoboard. When active, the current VME cycle requests the contents of the *Control and Status Register*.

## **EOPCycleUL**

This signal is low-active, is generated on the protoboard and indicates to the Host Interface that the last word of the packet being transmitted to the ring network has been transferred.

#### **BSysResetL**

This signal is low-active and is the buffered version of the VME system reset. It is subsequently mousetrapped on the system board.

#### BDS0L, BDS1L

These signals are the buffered version of the VME Data Strobes. They are subsequently mousetrapped on the system board.

#### SysIACKINL

This signal is low-active and is generated on the protoboard. It indicates that the host is acknowledging the interrupt request of the Host Interface.

## SysIRQ2L

This low-active signal is generated on the system board and is buffered to become the VMEbus interrupt request line 2 on the protoboard.

# **SysDTACK**

This high-active signal is generated by the system board and is used to generate the VMEbus Data Acknowledge on the protoboard.

## **ALIVE**

This high-active signal is generated on the system board and indicates that the system board is operational.

| Signal Name | Connector J1<br>Pin Number | Signal Name | Connector J1<br>Pin Number |

|-------------|----------------------------|-------------|----------------------------|

| D[0]        | A1                         | D[16]       | A17                        |

| D[1]        | A2                         | D[17]       | A18                        |

| D[2]        | A3                         | D[18]       | A19                        |

| D[3]        | A4                         | D[19]       | A20                        |

| D[4]        | A5                         | D[20]       | A21                        |

| D[5]        | A6                         | D[21]       | A22                        |

| D[6]        | A7                         | D[22]       | A23                        |

| D[7]        | A8                         | D[23]       | A24                        |

| D[8]        | A9                         | D[24]       | A25                        |

| D[9]        | A10                        | D[25]       | A26                        |

| D[10]       | A11                        | D[26]       | A27                        |

| D[12]       | A12                        | D[27]       | A28                        |

| D[12]       | A13                        | D[28]       | A29                        |

| D[13]       | A14                        | D[29]       | A30                        |

| D[14]       | A15                        | D[30]       | A31                        |

| D[15]       | A16                        | D[31]       | A32                        |

|             |                            |             |                            |

| Signal Name  | Connector J2<br>Pin Number | Signal Name  | Connector J2<br>Pin Number |

|--------------|----------------------------|--------------|----------------------------|

| GND          | A1                         | RdCSRCycleUL | A17                        |

| GND          | A2                         | GND          | A18                        |

| GND          | A3                         | EOPCycleUL   | A19                        |

| GND          | A4                         | GND          | A20                        |

| SysDTACK     | A5                         | BDS0L        | A21                        |

| GND          | A6                         | GND          | A22                        |

| SysIRQ2L     | A7                         | BDS1L        | A23                        |

| GND          | A8                         | GND          | A24                        |

| ALIVE        | A9                         | BSysResetL   | A25                        |

| GND          | A10                        | GND          | A26                        |

| WrPktCycleUL | A11                        | SysIACKINL   | A27                        |

| GND          | A12                        | GND          | A28                        |

| RdPktCycleUL | A13                        | GND          | A29                        |

| GND          | A14                        | GND          | A30                        |

| WrCSRCycleUL | A15                        | GND          | A31                        |

| GND          | A16                        | GND          | A32                        |

Pins B1-B32 are connected to GND on both connectors.

Figure 1

# 1.2.2 Functional Description

The Host Interface is memory-mapped into the Sun-4's address space and occupies eight contiguous addresses within that space. Each of the Host Interface's "addresses" corresponds to a specific function to be performed by the HIF. These functions include: write packet data, read packet data, write the Control and Status Register, read the Control and Status Register, and indicate that the last word of a data packet has been written.

The Host Interface has one *port* to the ring network, implemented as separate *transmit* and *receive interfaces*. The packet transfer scheme of the multi-ring is supported by the host interface. Thus, data is transferred between the ring network and the host in the form of packets comprised of a destination address followed by zero or more data words.

Also contained on the HIF is the circuitry for interrupting the host under certain conditions. These conditions are: receiving an entire packet from the ring, acquiring a channel for data transmission by the ring network, and detecting a receive buffer overflow. *Interrupt Request Line* 2 of the VMEbus is used to alert the host to one (or more) of these conditions. The host must read the *Host Interface Control and Status Register* to determine the cause of the interrupt.

The Host Interface contains a Control and Status Register (CSR) which contains information about the status of data transfers, status of the ring network, and the setting of HIF control parameters (See Section 1.6). A special register on the prototype board, the Test Register, is used exclusively for intitial debug of the Host Interface (See Section 1.7).

# 1.3 Memory Map

The Host Interface is memory-mapped into the Sun-4 and occupies eight (8) contiguous addresses within a page of memory. The upper (19) nineteen VMEbus address bits define which page is mapped to the HIF and are selected by switches on the HIF VME board. Since address bits 5 through 12 are not specified in the HIF address map, the eight addresses are duplicated throughout the page.

The host accesses the Host Interface by performing memory read or write cycles to an address within the HIF memory map. The HIF monitors the address lines and the address modifier lines of the VMEbus and performs the appropriate function when the HIF is the target of a particular cycle. The functions or commands that correspond to the HIF addresses are as follows:

| A31-A13  | A12-A5 | A4A3A2 | Address Modifier | WriteL* | Function            |

|----------|--------|--------|------------------|---------|---------------------|

|          |        |        | (Hex)            |         |                     |

| HIF Page | X      | 000    | 09,0A,0D,0E      | 0       | Write Packet Data   |

| HIF Page | X      | 000    | 09,0A,0D,0E      | 1       | Read Packet Data    |

| HIF Page | X      | 001    | 09,0A,0D,0E      | 0       | End of Packet       |

| HIF Page | X      | 001    | X                | 1       | Reserved            |

| HIF Page | X      | 010    | 09,0A,0D,0E      | 0       | Write CSR Data      |

| HIF Page | X      | 010    | 09,0A,0D,0E      | 1       | Read CSR Data       |

| HIF Page | X      | 011    | 09,0A,0D,0E      | 0       | Write Test Register |

| HIF Page | X      | 011    | 09,0A,0D,0E      | 0       | Read Test Register  |

| HIF Page | X      | 1XX    | X                | X       | Reserved            |

Table 1

As indicated by the Address Modifier bits, the HIF only responds to non-block transfer cycles. 'X' = don't care. 'HIF Page' corresponds to the page in memory assigned to the Host Interface. WriteL\* is the VMEbus signal that indicates the direction of data transfer: it is high for transfers from the Host Interface and low for transfers to the Host Interface.

## 1.4 Transmit Control

# 1.4.1 Transferring the Destination Address

When the host executes the "Write Packet Data" command, the VME protoboard activates the signal WrPktCycleUL. In response, the system board activates EnbTxDatL to enable D[0:31] through the system board data buffers to the TxDat bus, and sets the XferPend bit of the Control and Status Register. Two cycles later, the system board latches the VME data so that the VME cycle can be terminated. The system board's transmit logic then asserts TxReadyL, indicating to the ring network that the destination address of the packet is on the TxDat bus and has been valid for the two previous cycles. Also asserted in this cycle is TxDTACKL, which causes the assertion of the VME data transfer acknowledge signal, DTACKL, and thus indicates to the host the receipt of the data. Once the mousetrapped data strobe signals LDSOL and LDSIL are detected high, the transmit control logic de-asserts TxDTACKL(causing DTACKL be de-asserted). TxReadyL remains active.

# 1.4.2 Acquiring the Receiver and A Channel

Once the host has transferred the destination address of a packet to the Host Interface, it must wait for the ring network to acquire the intended receiver and a channel. When the ring network indicates it is ready for the data transmission by asserting TxGo, the HIF system board de-asserts XferPend and sets the RingRdy bit. The host may become aware of the "ring ready" condition in one of two ways. If IntEnb1 of the CSR is set, the host will be interrupted once TxGo is asserted. Otherwise, the host must poll the CSR to check the RingRdy bit. If the former is the case, the interrupt control logic will assert SysIRQ2L (causing IRQ2L to be asserted) coincident with setting RingRdy. The host will eventually acknowledge the interrupt and will request status/ID information from the Host Interface. In response, the HIF transfers a word that contains its device identification and de-asserts the Interrupt Request Line. During the interrupt acknowledge sequence, the host interface prevents further interrupts by clearing IntEnb0, IntEnb1, and IntEnb2. The host may then ascertain the cause of the interrupt by reading the CSR.

# 1.4.3 Transferring Data Words

Once the RingRdy bit has been set, the host may transfer the packet data. When the host executes the "Write Packet Data" command, the VME board activates the signal WrPktCycleUL. Upon receipt of the mousetrapped signal WrPktL, the transmit control circuitry enables D[0:31] onto the TxDat bus by activating EnbTxDatL. During this cycle the system board logic also asserts TxPut to indicate to the ring network that valid data will be placed on the data bus during the next cycle. TxPut is de-asserted on the following cycle. Two cycles later, TxDTACKL goes low, causing the assertion of the VMEbus data transfer acknowledge signal and thus terminating the VME cycle. Once LDSOL and LDSIL go high, TxDTACKL (and thus DTACKL) and EnbTxDatL are deasserted. The host must execute a "Write Packet Data" command for each word of the packet. The transmit control circuitry holds TxReadyL low and asserts TxPut prior to each cycle in which a data word is transferred.

# 1.4.4 Indicating the End of the Packet

Once all words of the packet have been transferred to the Host Interface (and thus to the ring network as well), the host executes the "End of Packet" command. The VME board will activate the signal EOPCycleUL. Upon receipt of the mousetrapped signal EOP, the transmit control circuitry de-asserts TxReadyL since all words of the packet have been transferred, resets the RingRdy bit, and asserts TxDTACKL. Assertion of TxDTACKL causes the assertion of the VMEbus data transfer acknowledge signal. When the system board logic detects LDSOL and LDSIL high, indicating that the host has terminated the VMEbus cycle, TxDTACKL is de-asserted (and thus DTACKL is also de-asserted).

## 1.5 Receive Control

### 1.5.1 Host Interface Receive Buffers

When the host interface receives data from the ring network, it stores the information in one of its receive buffers. Each of the two Host Interface receive buffers is 32-bits wide, 16K words deep and may contain the data for a single packet. Data from the ring network may be written into one buffer while data is read from the other buffer by the host. A maximum of two packets may be stored in the receive buffers before the host reads the contents of one buffer. The switching of read and write operations between the buffers is transparent to the host.

Associated with each buffer is a 16Kx1 "latch" which is used to keep track of the end of a packet; the ring signal RxTail is written into this "latch". Also associated with each receive buffer are address counters which are incremented each time a word is written into or read from the buffer. When an entire packet has been written into a buffer, the packet word counter contains the number of words stored in that buffer, including the destination address of the packet. If the ring network attempts to write more than 16K words into either buffer, the BufOvrFlA(B) signal is activated, and BufOvrFl is also activated. If the corresponding interrupt bit of the CSR, IntEnb2, is set, the interrupt request line to the host is asserted due to the buffer overflow. The buffer overflow bits remain asserted until the ring network is rebooted.

There are three status bits internal to the receive control state machine. Two of these bits (BufStatA and BufStatB) indicate whether the buffers contain entire, unread packets, and one (LRW) indicates which of the buffers contains the least-recently written packet. If both buffers are empty when a packet is received from the ring network, the packet is placed in Buffer A; BufStatA is set and the LRW bit is cleared once the entire packet has been written into the buffer. BufStatB is set when an entire packet has been written into Buffer B. The following chart indicates the possible values of the status bits and the corresponding status of the two receive buffers:

| BufStatA | BufStatB | LWR | Status                                                                       |

|----------|----------|-----|------------------------------------------------------------------------------|

| 0        | 0        | 0   | Neither buffer contains an entire packet                                     |

| 0        | 0        | 1   | Not valid                                                                    |

| 0        | 1        | 0   | Buffer B contains an entire packet                                           |

| 0        | 1        | 1   | Not valid                                                                    |

| 1        | 0        | 0   | Buffer A contains an entire packet                                           |

| 1        | 0        | 1   | Not valid                                                                    |

| 1        | 1        | 0   | Both buffers contain an entire packet; Buffer A packet was received first    |

| 1        | 1        | 1   | Both buffers contain an entire packet;<br>Buffer B packet was received first |

Table 2

# 1.5.2 Writing Data into the Receive Buffers

When one (or both) of the the receive buffers is empty, the HIF receive control circuitry asserts the ring network signal RxReadyL to indicate that it can receive a packet of length 16K words. The system board logic also asserts the signal CSAWrL or CSBWrL, depending upon which buffer is empty. If both are empty, the data will be placed in Buffer A, as described above. CSAWrL causes the chip-select line to the Buffer to be asserted. EnbRxDatA(B)L is asserted during the same cycle to connect the ring network receive data (RxDat) with the I/O pins of the Buffer. Write-enable pulses are generated on clock cycles following the assertion of RxPut by the ring network. RxReadyL is de-asserted on the cycle following the assertion of RxPut and remains low while the packet is written into the Buffer.

The assertion of RxTail by the ring network indicates that the ring network has already transmitted the last word of that packet. Two cycles after the assertion of RxTail, EnbRxDatA(B)L is de-asserted. The high logic level on EnbRxDatA(B)L essentially disconnects the RxDat bus from the I/O pins of the Buffer. On the following clock cycle CSAWrL (or CSBWrL) is de-asserted, BufStatA(B) is asserted, and the PktPend bit of the CSR is set (if the bit is not already set).

# 1.5.3 Alerting the Host to the Receipt of a Packet

Once the entire packet has been latched into a receive buffer, the host may be interrupted. If the IntEnb0 bit of the Control and Status Register is set, the interrupt control logic asserts Interrupt Request Line 2 on the VMEbus. The host's interrupt handler will eventually acknowledge the interrupt request by setting the lower three address bits to binary '010' (corresponding to interrupt request line 2) and asserting IACKINL. When the interrupt control circuitry detects low levels on SysIACKINL and the mousetrapped signal LDSOL, it de-asserts the interrupt request. EnbIntStatL is asserted during the same cycle to enable the status/id word onto the VME data bus. This word identifies the interrupting device to the host and is defined by the switches of Switch Bank 1. The host interface clears IntEnb0, IntEnb1, and IntEnb2 to prevent further interrupts. On the following cycle, the interrupt control circuitry responds with IntDTACKL. causing DTACKL, the VMEbus data transfer acknowledge signal, to be asserted. Eventually the interrupt handler of the host will terminate the interrupt acknowledge sequence by driving DSOL high. The Host Interface system board logic de-asserts EnbIntStatLwhen it detects LDSOL high. On the following cycle, IntDTACKL is de-asserted, causing DTACKL to be de-asserted. The host may verify the cause of the interrupt by reading the Host Interface's Control and Status Register. If no other interrupt conditions exist, such as a buffer overflow, the host may begin to read the packet from the Buffer.

# 1.5.4 Reading the Word Count from the Receive Buffer

Since there is no indication of packet length inherent in the structure of the packet, the host must read the value stored in the packet word counter. The host executes a "Read Packet Data" cycle and receive control circuitry asserts EnbBufCntAL (or EnbBufCntBL). Thus, the packet length, or word count, is enabled onto the VMEbus. During the next clock cycle, RxDTACKL is asserted, resulting in the assertion of DTACKL. Of course, DTACKL signals the host that the data requested is currently available on the VME data bus. Eventually the host will terminate the transfer and LDSOL and LDSIL will go high. The receive logic de-asserts EnbBufCntAL in response and on the next cycle de-asserts RxDTACKL. De-assertion of RxDTACKL causes de-assertion of the VMEbus data transfer acknowledge signal DTACKL. EnbRxAddrAL (or EnbRxAddrBL) is asserted during this cycle as well.

# 1.5.5 Reading the Packet from the Receive Buffer

Once the word count of the packet has been transferred to the host, the actual contents of the packet may be read. The host executes another "Read Packet Data" command, causing the assertion of the RdPktL signal. In response to RdPktL, the receive control circuit asserts CSARdL (or CSBRdL) and thus asserts CSAL, the Receive Buffer chip select line. The Buffer output enable, OEAL, is also asserted during this cycle. Since EnbRxAddrAL is still asserted, the data from the Buffer is enabled onto the VME data bus shortly after the high-to-low transition of CSAL. Two cycles later, RxDTACKL, and ultimately DTACKL, is asserted, indicating to the host that the data requested is currently available on the bus. Once the host terminates the data transfer by driving DSOL and DS1L high, CSARdL and OEAL transition to a high logic level. On the following cycle RxDTACKL is de-asserted, causing the VMEbus data transfer acknowledge signal, DTACKL, to be de-asserted. This sequence of events is repeated for each word of the packet. Each time a word is read from the Buffer, the address counter increments the buffer's addresss.

# 1.5.6 Reading the Last Word of the Packet

Each time a word is read from a Buffer, the contents of the associated "tail latch," TailBitA(B), are also read. When the TailBitA(B) is detected to be '1', the Buffer's address counters are cleared, BufStatA(B) is cleared and PktPend is cleared if BufStatB(A) is not set.

The host must read the *Control Status Register* after the entire packet has been read to determine whether a packet is stored in the other receive buffer. Interrupts should be enabled if no interrupt conditions exist.

If the host driver attempts to read more words than are contained in a particular packet and a packet is latched into the other Buffer, the HIF will transfer the packet word count and the contents of the other packet erroneously. If the other buffer is empty or only part of a packet has been received, the VMEbus cycle is acknowledged, but no data is transferred to the host.

# 1.6 Host Interface Control and Status Register (CSR)

# 1.6.1 CSR General Description

The Control and Status Register is a 32-bit register which contains information about the status of the Host Interface board, the ring, transfers to the ring, and the setting of certain control parameters. All bits except ResetGenL are reset during the ring-boot sequence and on power-up. Bit 0 is the least significant bit.

#### Bit 0:

IntEnb0 When set to '1', the interrupt circuitry of the Host Interface activates the interrupt request line when an entire data packet has been received. When set to '0', this condition does not cause an interrupt request.

#### Bit 1:

IntEnb1 When set to '1', the interrupt circuitry of the Host Interface activates the interrupt request line once the ring network has acquired a channel for data transmission. When reset to '0', this condition does not cause an interrupt request.

#### Bit 2:

IntEnb2 When set to '1', the interrupt circuitry of the Host Interface activates the interrupt request line if BufOvrFl becomes activated. When reset to '0', the buffer overflow condition does not cause an interrupt.

#### Bit 3:

ResetGenL When this bit is low, the HIF activates ring interface signal ResetGenL When set to '1', Reset GenL is high.

#### Bit 4:

PktPend The Host Interface sets this bit to '1' when a data packet has been received from the ring network and written into one of the receive buffers. This bit is reset when the contents of both receive buffers have been read by the host.

#### Bit 5:

XferPend When this bit is set, the HIF has requested a transfer to the ring network and is awaiting an acknowledgement from the ring network.

#### Bit 6:

RingRdy When this bit is set, the HIF has acquired a ring network channel for data transmission.

#### Bit 7:

PktCntNxt When set, this bit indicates that if a "Write Packet Data" cycle is executed and at least one of the buffers contains a packet (PktPend = 1), the data transferred will be the packet word count.

### Bit 8:

**BufOvrFl** This bit is set if the ring network attempts to write more than 16K words into either of the receiver buffers. The bit remains set until the ring network is rebooted.

Bits 9-31:

Reserved

### 1.6.2 Reading the Control and Status Register

The host may read the contents of the CSR by executing the "Read CSR" command. The protoboard logic will assert RdCSRCycleUL in response, and register control logic asserts EnbCSRDatL as a result. The Control And Status Register data is enabled onto the VME data bus by EnbCSRDatL and occupies the lower 9 bits. On the next clock cycle, the register control logic signals the host that the data on the VMEbus is valid by asserting CSRDTACKL (the VME data transfer acknowledge signal DTACKL is asserted due to CSRDTACKL). The host terminates the transfer by driving DSOL and DS1L high, causing the mousetrapped versions of these signals to go high and ultimately causing the register control logic to de-assert EnbCSRDatL. On the next cycle, CSRDTACKL is de-asserted, causing DTACKL to be de-asserted to terminate the cycle.

### 1.6.3 Writing the Control and Status Register

The host may write bits 0-3 of the Control and Status Register by executing a "Write CSR" command. The host must place the values to be written on the three least significant bits of the data bus, with the least significant bit corresponding to the value to be written for IntEnb0. The protoboard address decode logic asserts WrCSRCycleUL in response to the command. The double-latched version of this signal initiates the write sequence in the control logic. RegCLK is asserted on the next clock cycle to latch the lower three bits of the D[0:31] data bus. It is de-asserted on the following cycle simultaneous with the assertion of CSRDTACKL. Assertion of CSRDTACKL causes the VMEbus data acknowledge (DTACKL) to be asserted and thus indicates to the host that the bus data has been written. The host eventually terminates the cycle due to DTACKL and drives DSOL and DSIL high. When LDSOL and LDSIL are both high, CSRDTACKL is deasserted, causing DTACKL to be de-asserted.

# 1.7 Test Register

A special register, the *Test Register*, physically resides on the prototype board. The *Test Register* is a 32-bit read-write register that can be used in the initial stages of debug. This register is accessed by executing the "Write Test Register" and "Read Test Register" commands with Jumper 1 set to position 3-1. Jumper 1 also resides on the prototype board and should be set to position 3-5 for normal operation. This register contains no meaningful information and will contain random values upon power-up.

# 1.8 Boot Sequence

The Host Interface board and the host driver are responsible for booting Pixel-planes5 ring network. When the driver is ready for the host interface to boot the multi-ring, it executes the "Write CSR" command with bit 3 of the data bus set to '0'. This command causes the ResetGenL signal to the ring network to be asserted; the ring network in turn asserts the network reset signal, DevReset. (Details of how the CSR is written are contained in Section 1.6.3.) After at least 12.5 µsecs, the host executes another "Write CSR" command in order to set ResetGenL to '1'. Bit 3 of the data bus should be set to '1' during this command. All system board circuitry (except that associated with the booting of the ring network) is reset by DevReset from the ring during the boot sequence.

## 1.9 Special Conditions

The Host Interface hardware is designed to minimize the chances of the host crashing due to faulty software and to allow the host to operate with an installed protoboard when the rest of the Pixel-planes5 system is not operational.

If host software attempts to access one of the locations within the Host Interface memory map that is *reserved*, logic on the protoboard will activate *DTACKL*, the VMEbus data transfer acknowledge signal, to terminate the VME cycle. Activating *DTACKL* prevents a "time-out" on the VMEbus. No valid data is transferred during such cycles.

If a protoboard is installed in the host but the remainder of the Pixel-planes5 system is not operational, the protoboard will generate the data transfer acknowledge signal, DTACKL, in response to any VME access within the Host Interface page. By acknowledging the cycle, the Host Interface prevents a "time-out" on the VMEbus. Of course, no valid data is transferred during the access. The protoboard also generates IACKOUTL, the daisy-chain interrupt acknowledge signal, when the rest of the system is not "alive". In this case, the protoboard merely passes the falling edge of its IACKINL line to IACKOUT L to complete the daisy-chain.

# Chapter III.2 GRAPHICS PROCESSOR

# III.2.1 Graphics Processor Specification

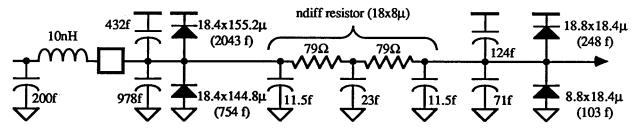

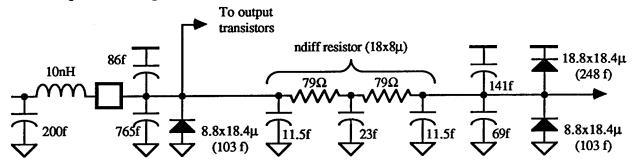

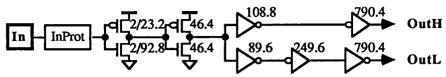

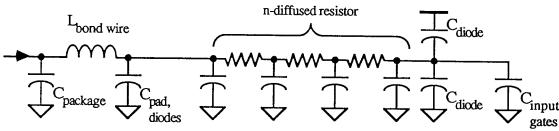

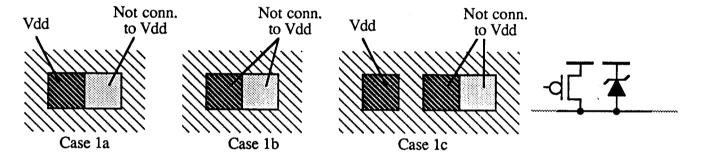

The Pixel-Planes 5 primary design goal of one million Phong-shaded triangles per second requires approximately 250 MFLOPS in front-end performance. We meet this requirement with a MIMD array of up to 16 (or more) floating-point engines called *Graphics Processors* (GPs).

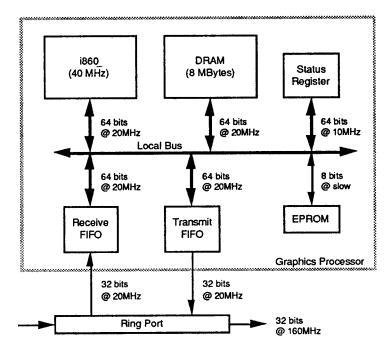

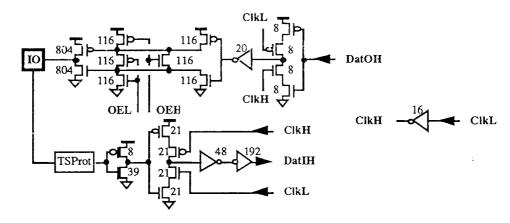

A Graphics Processor consists of an Intel i860 CPU, 8 MB of DRAM memory, and a ring interface. The ring interface occupies one ring node, and allows devices on other ring nodes to send programs and data to the GP, and to receive data from it. The GP consists of six main modules: the i860 CPU, its DRAM memory, a ring transmit interface, a ring receive interface, a status register, and an EPROM for booting the i860. Figure 1 shows the block diagram of a Graphics Processor.

Figure 1. Graphics Processor block diagram.

### III.2.1.1 Intel i860 Microprocessor

This subsection gives a brief overview of the Intel i860 Microprocessor, the heart of the GP design. For more information, see the i860 64-Bit Microprocessor Data Sheet, the i860 64-Bit Microprocessor Programmer's Reference Manual, or the i860 64-Bit Microprocessor Hardware Reference Manual.

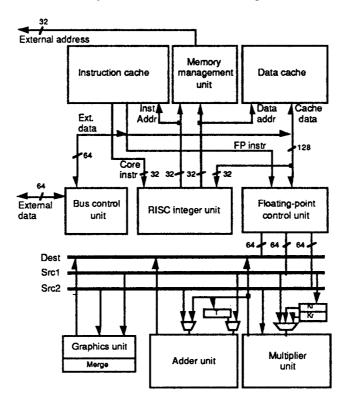

The i860 is a 64-bit RISC microprocessor with integrated code and data caches. Internally, it

contains a RISC integer processor and a 64-bit floating-point processor. The processor runs at 40 MHz and can perform an integer operation and a floating-point operation (potentially a multiply/accumulate) every 40 MHz clock cycle. This gives it a peak processing speed of 40 integer MIPS and 80 MFLOPS. Figure 2 shows a block diagram of the i860 Microprocessor.

Figure 2. Block diagram of the i860 Microprocessor.

The integer processor controls overall operation of the i860. It executes load, store, integer, and control-transfer instructions and fetches instructions for the floating-point processor. It contains a set of 32 32-bit registers. It has a trap mechanism that allows it to rapidly respond to software-initiated and externally-initiated traps and interrupts. Virtual memory is supported with a 64-entry, four-way set-associative memory called the *Translation Lookaside Buffer* (TLB). When paging is enabled, the i860 uses the TLB to translate logical addresses to physical addresses and to check for access violations. Both user and supervisor privilege levels are provided.

The floating-point processor contains a 64-bit floating-point adder, a 64-bit floating-point multiplier, and a 64-bit parallel graphics unit. It has an additional set of dedicated registers, which can be accessed as 32 32-bit registers or 16 x 64-bit registers. In addition, special load and store instructions allow four adjacent 32-bit registers to be loaded from or stored to cache simultaneously. All floating-point and graphics instructions use these registers as their source and destination operands. Graphics instructions make use of a special, parallel integer unit that allows multiple additions and comparisons to be performed in parallel. Floating-point and graphics instructions have a latency of 3-4 cycles, but generate a new result every clock cycle.

The instruction cache is a 4 KB two-way set-associative memory with 32-byte blocks. It transfers up to 64-bits per clock cycle to the instruction unit. The data cache is an 8 KB two-

way set-associative memory, also with 32-byte blocks. It transfers up to 64-bits per clock cycle to the integer unit and up to 128-bits per clock cycle to the floating-point unit. The data cache uses a write-back scheme. Caching can be inhibited by software where necessary.

The processor communicates with external memory and I/O devices via a 64-bit bus called the *local bus*. The local bus can initiate a new cycle every 50 nsec (two clock cycles). It is pipelined, allowing up to three bus cycles to be outstanding at once.

Address Map. The i860 local bus has a 32-bit address space. All memory and I/O devices must be mapped to this address space, since no separate provisions are made for I/O. Figure 3 describes the GP's address map. Notice that DRAM memory is mapped redundantly. The reasons for this are described in the following sections. This means, however, that different logical addresses may correspond to the same physical address.

| A31 <sup>1</sup> | A30-A27   | A26 | A25 | A24 | 1 | Device <sup>2</sup>      | Address (Addr[27:0]) <sup>3</sup> |

|------------------|-----------|-----|-----|-----|---|--------------------------|-----------------------------------|

| X                | 1         | 1   | 1   | 1   |   | EPROM/DRAM <sup>4</sup>  | F000000-FFFFFF                    |

| X                | 1         | 1   | 1   | 0   | 1 | DRAM (8 Mbytes)          | E000000-EFFFFFF                   |

| X                | 1         | 1   | 0   | 1   | i | DRAM w/ transmit FIFO    | D000000-DFFFFFF                   |

| X                | 1         | 1   | 0   | 0   | 1 | Receive FIFO             | C000000-CFFFFF                    |

| X                | 1         | 0   | 1   | 1_  | - | Status/Command Registers | B000000-BFFFFFF                   |

| X                | 1         | 0   | 1   | 0   | 1 | Unassigned               | A000000-AFFFFFF                   |

| X                | 1         | 0   | 0   | 1   | 1 | Unassigned               | 9000000-9FFFFF                    |

| X                | 1         | 0   | 0   | 0   | 1 | Unassigned               | 8000000-8FFFFF                    |

| X                | not all 1 | X   | X   | X   | 1 | Invalid                  | 0000000-7FFFFF                    |

<sup>&</sup>lt;sup>1</sup>A31 controls cache enabling and is not used for address decoding.

Figure 3. GP Address Map.

Address bit 31 is not used to decode addresses at all. This bit is used to control whether a memory cycle is to be cached or not. If A31 is 1, any date read during the bus cycle will not be cached. If A31 is 0, the data word is assumed to be cacheable. By setting A31 appropriately, software can control which data are cached, and which are always written to external memory (this is particularly important for I/O).

A reference to an unassigned or invalid address results in a bus error interrupt (BErrInt).

### III.2.1.2 DRAM Memory System

A Graphics Processor 8 MBytes of DRAM memory. The memory is 64 bits wide (to match the local bus) and contains four banks of 16 Motorola MCM514256 256K x 4 DRAM plastic ZIPs. The local bus accesses the memory system a maximum of one cycle every 50 nsec using fast page mode. DRAM pages are 512 words long, so as long as memory accesses do not cross page boundaries, the memory system can keep up with the i860's local bus.

<sup>&</sup>lt;sup>2</sup>All devices are assigned 16 Mbyte blocks. They are multiply mapped within these blocks

<sup>&</sup>lt;sup>3</sup>Address bits 30-27 all must be '1' for any valid address.

<sup>&</sup>lt;sup>4</sup>After booting the system from the EPROM, the DRAMs are remapped to this location.

DRAM refresh cycles are performed automatically in hardware every 12.8 µsec. They cost nothing if memory is not being accessed, and at worst cost 7 cycles every 249 cycles (2.8%).

### III.2.1.4 Ring Transmit Interface